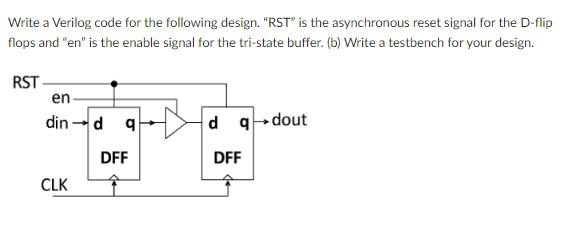

Question: Write a Verilog code for the following design. RST is the asynchronous reset signal for the D-flip flops and en is the enable signal

Write a Verilog code for the following design. "RST" is the asynchronous reset signal for the D-flip flops and "en" is the enable signal for the tri-state buffer. (b) Write a testbench for your design. RST- en- din-d q DFF CLK d qdout DFF

Step by Step Solution

There are 3 Steps involved in it

Lets start with an explanation of the Verilog code for the design In this code a module named DEFwithTriState is defined It has the following inputs a... View full answer

Get step-by-step solutions from verified subject matter experts