Question: Write a Verilog code in Xilinx ISE for a 32-bit signed multiplier using Booths algorithm for signed multiplication shown in the images below. Comment the

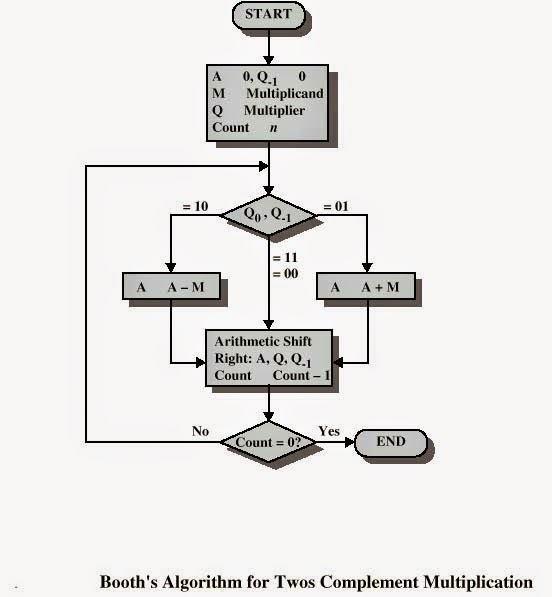

Write a Verilog code in Xilinx ISE for a 32-bit signed multiplier using Booths algorithm for signed multiplication shown in the images below. Comment the code to show how the Booth algorithm was implemented.

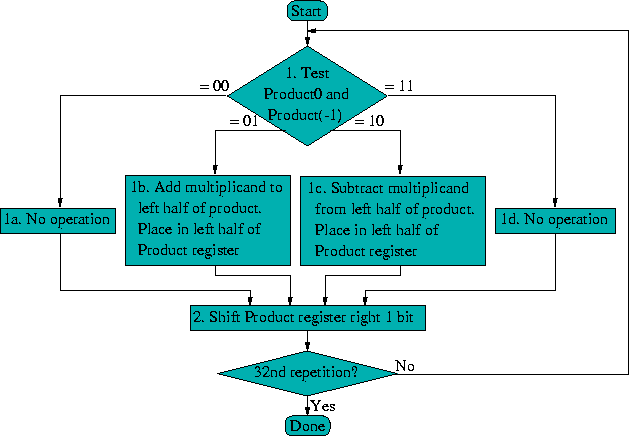

Start 1. Test Product0 and -or Product(-1 lb. Add multiplicand to c. Subtract multiplicand from left half of pcoduct.ld. No operatic Place in left half of Product register left half of product. ld. No operation la. No operationlace in left half of Product register 2. Shift Ptoduct tegister tight 1 bit No 32nd repetition? Yes Done Start 1. Test Product0 and -or Product(-1 lb. Add multiplicand to c. Subtract multiplicand from left half of pcoduct.ld. No operatic Place in left half of Product register left half of product. ld. No operation la. No operationlace in left half of Product register 2. Shift Ptoduct tegister tight 1 bit No 32nd repetition? Yes Done

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts