Question: Write Verilog code to create an arithmetic logic unit (ALU). The ALU must have two 32-bit input busses and must be able to perform addition,

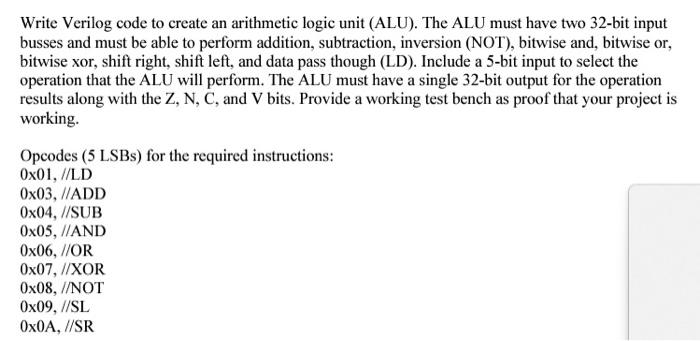

Write Verilog code to create an arithmetic logic unit (ALU). The ALU must have two 32-bit input busses and must be able to perform addition, subtraction, inversion (NOT), bitwise and, bitwise or, bitwise xor, shift right, shift left, and data pass though (LD). Include a 5-bit input to select the operation that the ALU will perform. The ALU must have a single 32-bit output for the operation results along with the Z,N,C, and V bits. Provide a working test bench as proof that your project is working. Opcodes (5 LSBs) for the required instructions: 001,//LD 0x03, //ADD 0x04, //SUB 0x05, //AND 006,//OR 0x07, //XOR 0x08, //NOT 009, //SL 0x0A,//SR Write Verilog code to create an arithmetic logic unit (ALU). The ALU must have two 32-bit input busses and must be able to perform addition, subtraction, inversion (NOT), bitwise and, bitwise or, bitwise xor, shift right, shift left, and data pass though (LD). Include a 5-bit input to select the operation that the ALU will perform. The ALU must have a single 32-bit output for the operation results along with the Z,N,C, and V bits. Provide a working test bench as proof that your project is working. Opcodes (5 LSBs) for the required instructions: 001,//LD 0x03, //ADD 0x04, //SUB 0x05, //AND 006,//OR 0x07, //XOR 0x08, //NOT 009, //SL 0x0A,//SR

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts