Question: You know that a Configurable Logic Block (CLB) in our FPGA is programmed to implement a combo logic function by loading a f/f register and

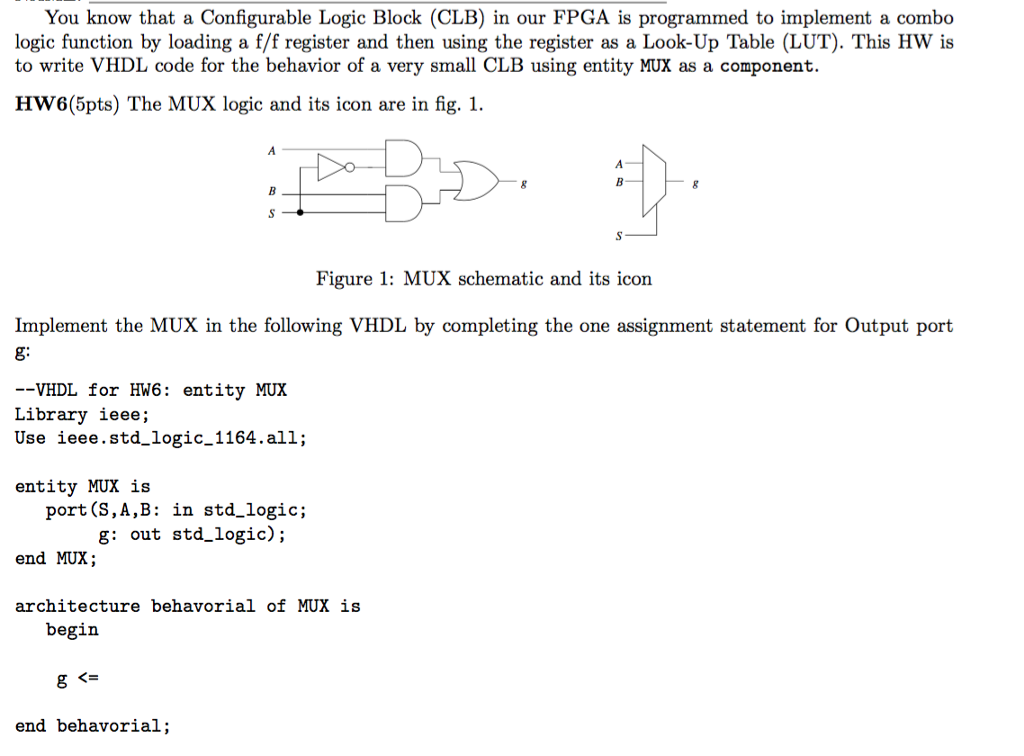

You know that a Configurable Logic Block (CLB) in our FPGA is programmed to implement a combo logic function by loading a f/f register and then using the register as a Look-Up Table (LUT). This HW is to write VHDL code for the behavior of a very small CLB using entity MUX as a component HW6 (5pts) The MUX logic and its icon are in fig. 1 58 Figure 1: MUX schematic and its icon Implement the MUX in the following VHDL by completing the one assignment statement for Output port g: VHDL for HW6: entity MUX Library ieee; Use ieee.std_logic 1164.all; entity MUX is port (S,A,B: in std.logic; g: out std_logic); architecture behavorial of MUX is begin g

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts