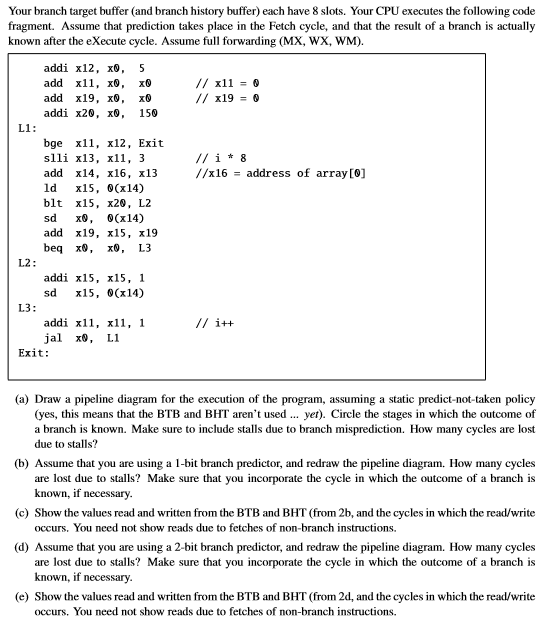

Question: Your branch target buffer (and branch history buffer) each have 8 slots. Your CPU executes the following code fragment. Assume that prediction takes place in

Your branch target buffer (and branch history buffer) each have 8 slots. Your CPU executes the following code fragment. Assume that prediction takes place in the Fetch cycle, and that the result of a branch is actually known after the eXecute cycle. Assume full forwarding (MX, WX, WM) addi x12, x, 5 add x11, x0, x add x19, x0, x addi x2, x 150 // x190 LI: bge x11, x12, Exit s111 x13, x11, 3 add x14, x16, x13 ld x15, 0(x14) blt x15, x20, L2 sd x0 0(x14) add x19, x15, x19 //x16 address of array [0] 2 addi x15, x15, 1 sd x15, 0(x14) L3: addi x11, x11, 1 jal x L1 Exit: (a) Draw a pipeline diagram for the execution of the program, assuming a static predict-not-taken policy (yes, this means that the BTB and BHT aren't used... yet). Circle the stages in which the outcome of a branch is known. Make sure to include stalls due to branch misprediction. How many cycles are lost due to stalls? (b) Assume that you are using a 1-bit branch predictor, and redraw the pipeline diagram. How many cycles are lost due to stalls? Make sure that you incorporate the cycle in which the outcome of a branch is known, if necessary (c) Show the values read and written from the BTB and BHT (from 2b, and the cycles in which the read/write occurs, You need not show reads due to fetches of non-branch instructions, (d) Assume that you are using a 2-bit branch predictor, and redraw the pipeline diagram. How many cycles are lost due to stalls? Make sure that you incorporate the cycle in which the outcome of a branch is known, if necessary Show the values read and written from the BTB and BHT (from 2d, and the cycles in which the read/write occurs. You need not show reads due to fetches of non-branch instructions. (e) Your branch target buffer (and branch history buffer) each have 8 slots. Your CPU executes the following code fragment. Assume that prediction takes place in the Fetch cycle, and that the result of a branch is actually known after the eXecute cycle. Assume full forwarding (MX, WX, WM) addi x12, x, 5 add x11, x0, x add x19, x0, x addi x2, x 150 // x190 LI: bge x11, x12, Exit s111 x13, x11, 3 add x14, x16, x13 ld x15, 0(x14) blt x15, x20, L2 sd x0 0(x14) add x19, x15, x19 //x16 address of array [0] 2 addi x15, x15, 1 sd x15, 0(x14) L3: addi x11, x11, 1 jal x L1 Exit: (a) Draw a pipeline diagram for the execution of the program, assuming a static predict-not-taken policy (yes, this means that the BTB and BHT aren't used... yet). Circle the stages in which the outcome of a branch is known. Make sure to include stalls due to branch misprediction. How many cycles are lost due to stalls? (b) Assume that you are using a 1-bit branch predictor, and redraw the pipeline diagram. How many cycles are lost due to stalls? Make sure that you incorporate the cycle in which the outcome of a branch is known, if necessary (c) Show the values read and written from the BTB and BHT (from 2b, and the cycles in which the read/write occurs, You need not show reads due to fetches of non-branch instructions, (d) Assume that you are using a 2-bit branch predictor, and redraw the pipeline diagram. How many cycles are lost due to stalls? Make sure that you incorporate the cycle in which the outcome of a branch is known, if necessary Show the values read and written from the BTB and BHT (from 2d, and the cycles in which the read/write occurs. You need not show reads due to fetches of non-branch instructions. (e)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts