Question: Your task in this project is hardware implementation of a tournament predictor ( which utilizes several dynamic branch predictors ) in VHDL or Verilog and

Your task in this project is hardware implementation of a tournament predictor which utilizes several dynamic branch predictors in VHDL or Verilog and compare their performance.

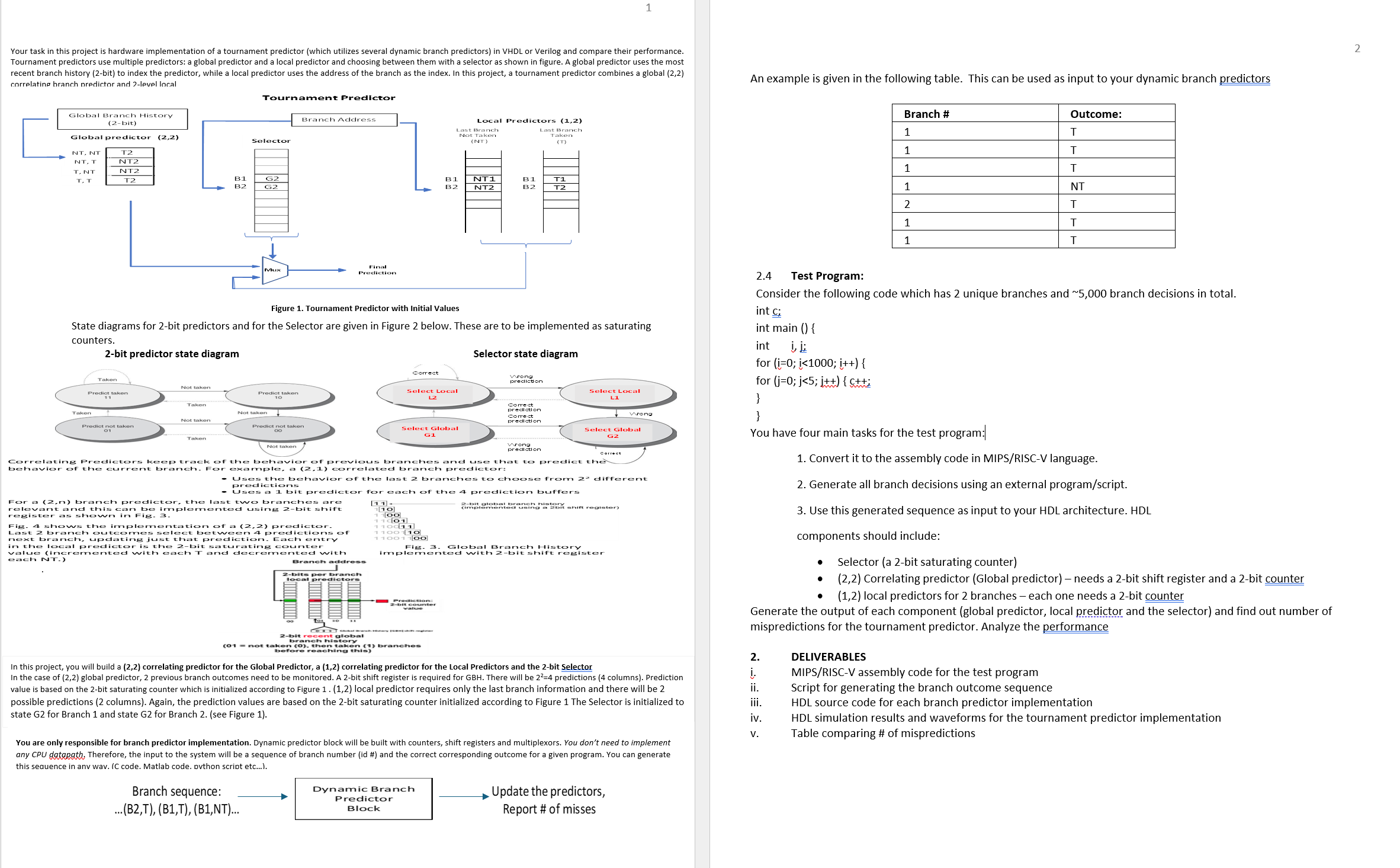

Tournament predictors use multiple predictors: a global predictor and a local predictor and choosing between them with a selector as shown in figure. A global predictor uses the most

recent branch history bit to index the predictor, while a local predictor uses the address of the branch as the index. In this project, a tournament predictor combines a global

rorrelating hranch nredictor and level local

Figure Tournament Predictor with Initial Values

State diagrams for bit predictors and for the Selector are given in Figure below. These are to be implemented as saturating

counters.

bit predictor state diagram

In this project, you will build a correlating predictor for the Global Predictor, a correlating predictor for the Local Predictors and the bit Selector

In the case of global predictor, previous branch outcomes need to be monitored. A bit shift register is required for GBH There will be predictions columns Prediction

value is based on the bit saturating counter which is initialized according to Figure local predictor requires only the last branch information and there will be

possible predictions columns Again, the prediction values are based on the bit saturating counter initialized according to Figure The Selector is initialized to

state G for Branch and state G for Branch see Figure

You are only responsible for branch predictor implementation. Dynamic predictor block will be built with counters, shift registers and multiplexors. You don't need to implement

any CPU datapath, Therefore, the input to the system will be a sequence of branch number id # and the correct corresponding outcome for a given program. You can generate

this seauence in anv wav. C code. Matlab code. ovthon script etc...

Branch sequence:

dots

Predictor

Update the predictors,

Report # of misses

An example is given in the following table. This can be used as input to your dynamic branch predictors

Test Program:

Consider the following code which has unique branches and branch decisions in total.

int ;

int main

int

for

for ;;

You have four main tasks for the test program:

Convert it to the assembly code in MIPSRISCV language.

Generate all branch decisions using an external programscript

Use this generated sequence as input to your HDL architecture. HDL

components should include:

Selector a bit saturating counter

Correlating predictor Global predictor needs a bit shift register and a bit counter

local predictors for branches each one needs a bit counter

Generate the output of each component global predictor, local predictor and the selector and find out number of

mispredictions for the tournament predictor. Analyze the performance

DELIVERABLES

i MIPSRISCV assembly code for the test program

ii Script for generating the branch outcome sequence

iii. HDL source code for each branch predictor implementation

iv HDL simulation results and waveforms for the tournament predictor implementation

v Table comparing # of mispredictions.

please try to answer the deliverable. main thing is i need verilog codescript

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock