Question: Zintel is a Semiconductor chip assembly and test factory in Woodlands where wafers are singulated , assembled and tested. The semiconductor chips are processed through

Zintel is a Semiconductor chip assembly and test factory in Woodlands where

wafers are singulated assembled and tested. The semiconductor chips are

processed through the machines in 'lots', Each lot contains a fixed number of

pieces or semiconductor chips known as lot size. The Zintel factory runs hours

a day, days a week throughout the year.

Assume that you are leading a project team to analyze the throughput parts

produced per unit time mean cycle time and Work in Process WIP at the Zintel

factory and to propose ways to improve the performance.

Assume that over the past few months, throughput at Zintel has averaged at

lots per day, Average WIP in the line has been lots. The line capacity can be

simplified as shown in Table

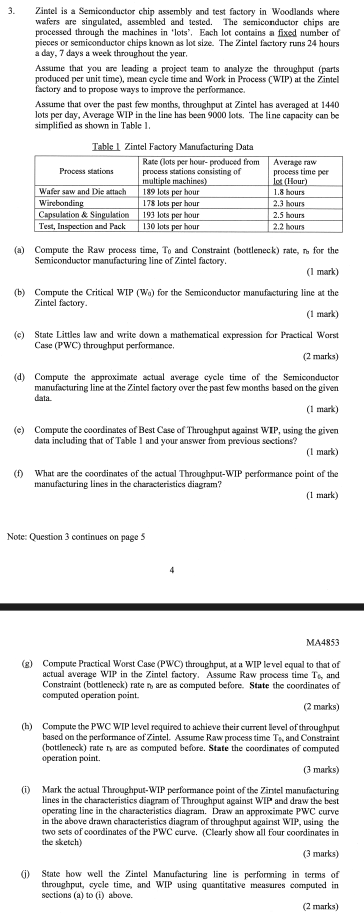

Table Zintel Factory Manufacturing Data

a Compute the Raw process time, and Constraint bottleneck rate, for the

Semiconductor manufacturing line of Zintel factory.

mark

b Compute the Critical WIP for the Semiconductor manufacturing line at the

Zintel factory.

mark

c State Littles law and write down a mathematical expression for Practical Worst

Case PWC throughput performanoe.

marks

d Compute the approximate actual average cycle time of the Semiconductor

manufacturing line at the Zintel factory over the past few months based on the given

data.

mark

e Compute the coordinates of Best Case of Throughput against WIP, using the given

data including that of Table I and your answer from previous sections?

mark

f What are the coordinates of the actual ThroughputWIP performance point of the

manufacturing lines in the characteristics diagram?

mark

Note: Question continues on page

g Compute Practical Worst Case PWC throughput, at a WIP level equal to that of

actual average WIP in the Zintel factory. Assume Raw process time and

Constraint bottleneck rate are as computed before. State the coordinates of

computed operation point.

marks

h Compute the PWC WIP level required to achieve their current level of throughput

based on the performance of Zintel. Assume Raw process time and Constraint

bottleneck rate are as computed before. State the coordinates of computed

operation point.

marks

i Mark the actual ThroughputWIP performance point of the Zintel manufacturing

lines in the characteristics diagram of Throughput against WIP and draw the best

operating line in the characteristics diagram. Draw an approximate PWC curve

in the above drawn characteristics diagram of throughput against WIP, using the

two sets of coordinates of the PWC curve. Clearly show all four coordinates in

the sketch

marks

j State how well the Zintel Manufacturing line is performing in terms of

throughput, cycle time, and WIP using quantitative measures computed in

sections a to i above.

marks

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock