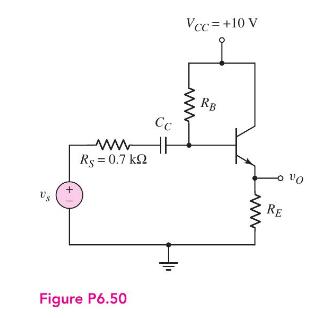

For the transistor in Figure P6.50, the parameters are (beta=100) and (V_{A}=infty). (a) Design the circuit such

Question:

For the transistor in Figure P6.50, the parameters are \(\beta=100\) and \(V_{A}=\infty\).

(a) Design the circuit such that \(I_{E Q}=1 \mathrm{~mA}\) and the \(Q\)-point is in the center of the dc load line.

(b) If the peak-to-peak sinusoidal output voltage is 4 \(\mathrm{V}\), determine the peak-to-peak sinusoidal signals at the base of the transistor and the peak-to-peak value of \(v_{s}\).

(c) If a load resistor \(R_{L}=1 \mathrm{k} \Omega\) is connected to the output through a coupling capacitor, determine the peakto-peak value in the output voltage, assuming \(v_{s}\) is equal to the value determined in part (b).

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen

Question Posted: