Question: The following code is executed by an ARM processor with each instruction executed exactly once: Show the contents of the instruction cache for these configurations,

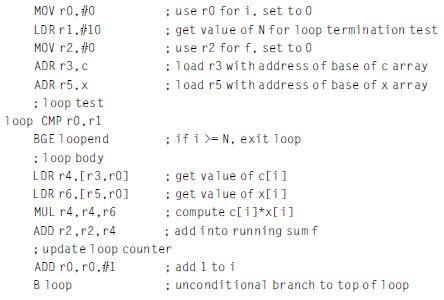

The following code is executed by an ARM processor with each instruction executed exactly once:

Show the contents of the instruction cache for these configurations, assuming each line holds one ARM instruction:

a. direct-mapped, two lines

b. direct-mapped, four lines

c. two-way set-associative, two lines per set

MOV ro. #0 LDR r1, #10 MOV r2.#0 ADR r3.c ADR r5.x : loop test loop CMP ro.rl BGE 1oopend : 1oop body LDR r4. [r3,r0] LDR r6.[5.0] MUL r4, r4r6 ADD r2.r2.r4 ; use r0 for 1, set to 0 : get value of N for loop termination test ; use r2 for f, set to 0 load r3 with address of base of carray. :load r5 with address of base of x array update loop counter ADD ro.ro.#1 B loop if i N, exit loop get value of c[i] get value of x[i] compute c[i]*x[1] add into running sum f ; add 1 to i : unconditional branch to top of loop

Step by Step Solution

3.18 Rating (148 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts