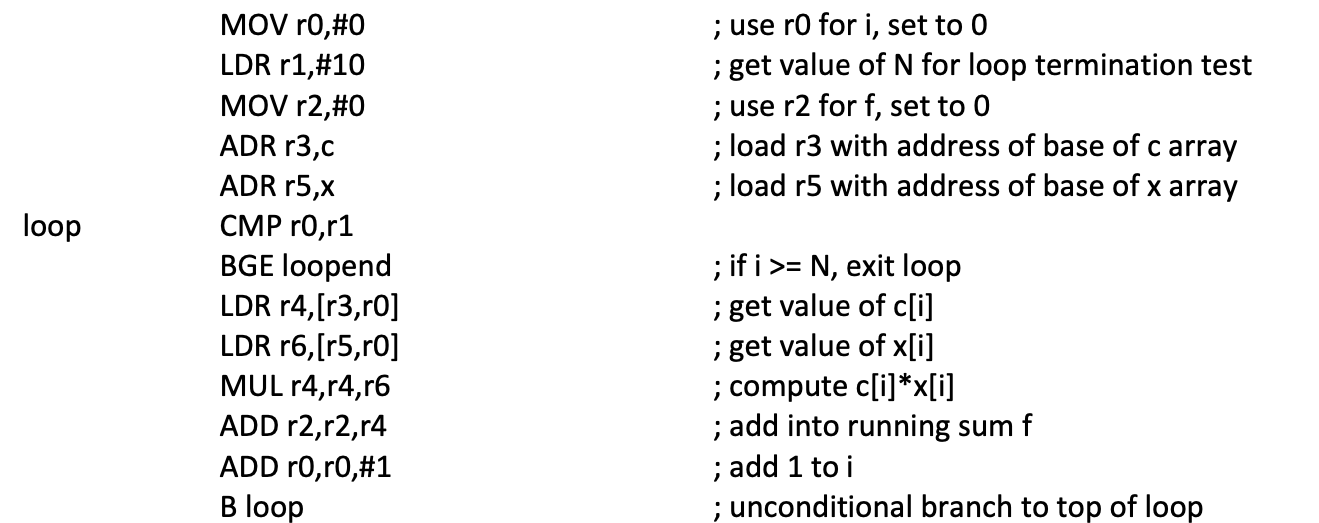

Question: Consider that the below code is executed by an ARM processor with each instruction executed exactly once. For the sake of simplicity, the following assumptions

Consider that the below code is executed by an ARM processor with each instruction executed exactly once. For the sake of simplicity, the following assumptions are made:

1. 2. 3. 4. 5.

The main memory has size of 4Gb. The size of the cache memory is 256 bytes. The size of each instruction is 16 bits. Each memory read operation returns 4 bytes. Assume the base address for the following code segment is 0x08000160.

Show the content of the cache memory upon the execution of each instruction presented

above, when:

1.A direct-mapped cache memory is used.

2.A 2-way set-associative cache memory is used.

MOVr0,#0LDRr1,#10MOVr2,#0ADRr3,cADRr5,xCMPr0,r1BGEloopendLDRr4,[r3,r0]LDRr6,[r5,r0]MULr4,r4,r6ADDr2,r2,r4ADDr0,r0,#1Bloop;user0fori,setto0;getvalueofNforloopterminationtest;user2forf,setto0;loadr3withaddressofbaseofcarray;loadr5withaddressofbaseofxarray;ifi>=N,exitloop;getvalueofc[i];getvalueofx[i];computec[i]x[i];addintorunningsumf;add1toi;unconditionalbranchtotopofloop

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts