Question: Consider the following code, which multiplies two vectors that contain single-precision complex values: Assume that the processor runs at 700 MHz and has a maximum

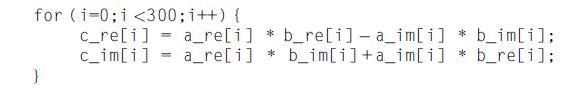

Consider the following code, which multiplies two vectors that contain single-precision complex values:

Assume that the processor runs at 700 MHz and has a maximum vector length of 64. The load/store unit has a start-up overhead of 15 cycles; the multiply unit, 8 cycles; and the add/subtract unit, 5 cycles.

a. What is the arithmetic intensity of this kernel? Justify your answer.

b. Convert this loop into RV64V assembly code using strip mining.

c. Assuming chaining and a single memory pipeline, how many chimes are required? How many clock cycles are required per complex result value, including start-up overhead?

d. If the vector sequence is chained, how many clock cycles are required per complex result value, including overhead?

e. Now assume that the processor has three memory pipelines and chaining. If there are no bank conflicts in the loop’s accesses, how many clock cycles are required per result?

for (i=0; i

Step by Step Solution

3.42 Rating (165 Votes )

There are 3 Steps involved in it

Lets go through each part of the question step by step a What is the arithmetic intensity of this kernel Justify your answer Arithmetic intensity is defined as the number of floatingpoint operations p... View full answer

Get step-by-step solutions from verified subject matter experts