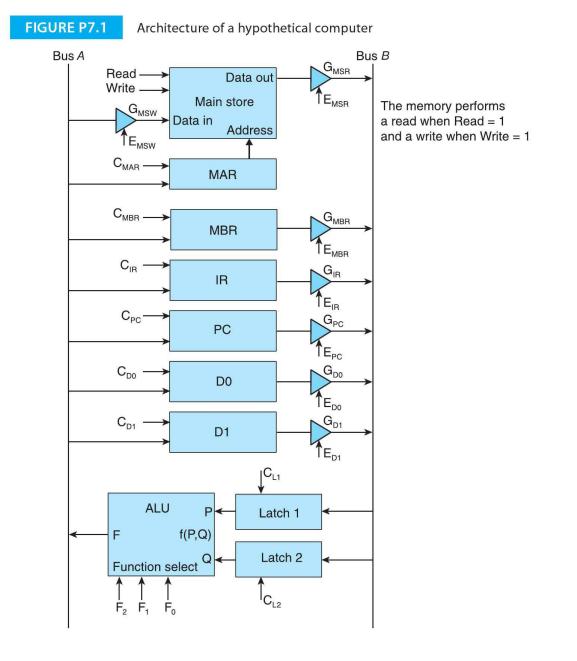

Question: This question asks you to implement register indirect addressing. For the architecture of Figure P7.1 , write the sequence of signals and control actions necessary

This question asks you to implement register indirect addressing. For the architecture of Figure P7.1 , write the sequence of signals and control actions necessary to execute the instruction ADD (Dl), DO that adds the contents of the memory location pointed at by the contents of register Dl to register DO, and deposits the results in DO. This instruction is defined in RTL form as [DO] .- [ [Dl]] + [DO].

FIGURE P7.1 Bus A Architecture of a hypothetical computer Read- Write GMSW TEMSW CMAR CMBR CIR F Cpc COO Cp ALU Main store Data in Data out Function select P f(P.Q) Address MAR MBR IR PC DO D1 |CL1 Latch 1 Latch 2 GMSR TEMSA GMBR TEMBR GR TER Gpc TEPC Bus B Goo TED Got TEDI The memory performs a read when Read = 1 and a write when Write = 1

Step by Step Solution

3.47 Rating (160 Votes )

There are 3 Steps involved in it

Here we have to read the contents of a register use it as an address and read fro... View full answer

Get step-by-step solutions from verified subject matter experts