Question: Assume there is no forwarding in this pipelined processor. Indicate hazards and add NOP instructions to eliminate them. In this exercise, we examine how data

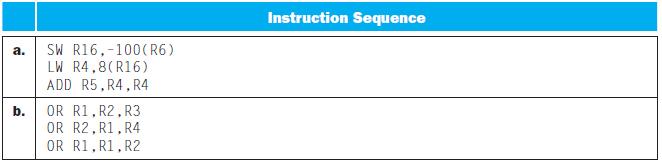

Assume there is no forwarding in this pipelined processor. Indicate hazards and add NOP instructions to eliminate them.

In this exercise, we examine how data dependences affect execution in the basic 5-stage pipeline described in Section 4.5. Problems in this exercise refer to the following sequence of instructions:

5 stage pipeline described in Section 4.5

The same principles apply to processors where we pipeline instruction execution. MIPS instructions classically take five steps:

1. Fetch instruction from memory.

2. Read registers while decoding the instruction. The regular format of MIPS instructions allows reading and decoding to occur simultaneously.

3. Execute the operation or calculate an address.

4. Access an operand in data memory.

5. Write the result into a register.

29 b. SW R16,-100 (R6) LW R4,8(R16) ADD R5, R4, R4 OR R1, R2, R3 OR R2, R1, R4 OR R1, R1, R2 Instruction Sequence

Step by Step Solution

3.41 Rating (145 Votes )

There are 3 Steps involved in it

In a pipelined processor without forwarding data hazards can lead to pipeline stalls where an instru... View full answer

Get step-by-step solutions from verified subject matter experts