Assuming that the L1 hit time determines the cycle times for P1 and P2, what are their

Question:

Assuming that the L1 hit time determines the cycle times for P1 and P2, what are their respective clock rates?

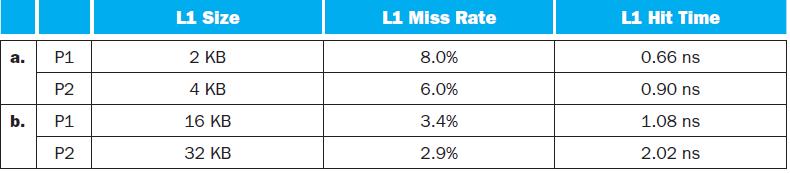

In this exercise, we will look at the different ways capacity affects overall performance. In general, cache access time is proportional to capacity. Assume that main memory accesses take 70 ns and that memory accesses are 36% of all instructions. The following table shows data for L1 caches attached to each of two processors, P1 and P2.

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Computer Organization And Design The Hardware Software Interface

ISBN: 9780123747501

4th Revised Edition

Authors: David A. Patterson, John L. Hennessy

Question Posted: