Question: Given this breakdown of execution cycles in the processor with direct support for the ADDM instruction, what speedup is achieved by replacing this instruction with

Given this breakdown of execution cycles in the processor with direct support for the ADDM instruction, what speedup is achieved by replacing this instruction with a 3-instruction sequence (LW, ADD, and then SW)? Assume that the ADDM instruction is somehow (magically) supported with a classical 5-stage pipeline without creating resource hazards.

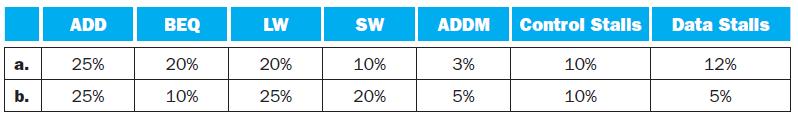

The remaining two problems in this exercise are about adding a new ADDM instruction to the ISA. In a processor to which ADDM has been added, these problems assume the following breakdown of clock cycles according to which instruction is completed in that cycle (or which stall is preventing an instruction from completing):

a. b. ADD 25% 25% BEQ 20% 10% LW 20% 25% SW 10% 20% ADDM Control Stalls 3% 5% 10% 10% Data Stalls 12% 5%

Step by Step Solution

3.51 Rating (158 Votes )

There are 3 Steps involved in it

To calculate the speedup achieved by replacing the ADDM instruction with a 3instruction sequence LW ... View full answer

Get step-by-step solutions from verified subject matter experts