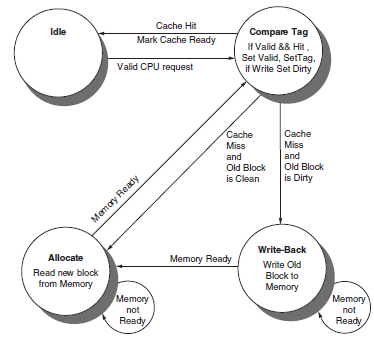

Question: In this exercise, we will explore the control unit for a cache controller for a processor with a write buffer. Use the finite state machine

Figure 5.40

1. What should happen if the processor issues a request that hits in the cache while a block is being written back to main memory from the write buffer?

2. What should happen if the processor issues a request that misses in the cache while a block is being written back to main memory from the write buffer?

3. Design a finite state machine to enable the use of a write buffer.×

Cache Hit Idle Compare Tag Mark Cache Ready If Valid && Hit, Set Valid, SetTag, if Write Set Dirty Valid CPU request Cache Cache Miss Miss and and Old Block is Dirty Old Block is Clean Memary Ready Write-Back Allocate Memory Ready Write Old Block to Memory Read new block from Memory Memory Memory not Ready not Ready

Step by Step Solution

3.36 Rating (159 Votes )

There are 3 Steps involved in it

1 The cache should be able to satisfy the request since it is otherwise idle when the write buffer i... View full answer

Get step-by-step solutions from verified subject matter experts