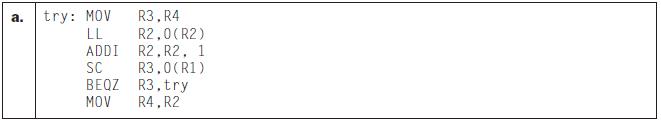

Question: The following table contains MIPS assembly code for a lock. Refer to the definition of the ll and sc pairs of MIPS instructions. For the

The following table contains MIPS assembly code for a lock. Refer to the definition of the ll and sc pairs of MIPS instructions.

For the load locked/store conditional code above, explain why this code may fail.

a. try: MOV LL ADDI SC BEQZ MOV R3, R4 R2,0 (R2) R2, R2, 1 R3,0 (R1) R3,try R4, R2

Step by Step Solution

3.48 Rating (155 Votes )

There are 3 Steps involved in it

The code youve provided seems to implement a simple form of a loadlocked LL and storeconditional SC pair for synchronization purposes The LL and SC in... View full answer

Get step-by-step solutions from verified subject matter experts