Question: What is the clock cycle time if we must support ADD, BEQ, LW, and SW instructions? In this exercise we examine how latencies of individual

What is the clock cycle time if we must support ADD, BEQ, LW, and SW instructions?

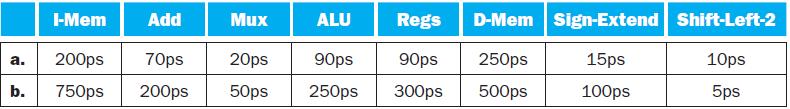

In this exercise we examine how latencies of individual components of the datapath affect the clock cycle time of the entire datapath, and how these components are utilized by instructions. For problems in this exercise, assume the following latencies for logic blocks in the datapath:

1-Mem Add 200ps b. 750ps a. Regs D-Mem Sign-Extend Shift-Left-2 90ps 250ps 15ps 10ps 250ps 300ps 500ps 100ps 5ps Mux 70ps 20ps 90ps 200ps 50ps ALU

Step by Step Solution

3.31 Rating (157 Votes )

There are 3 Steps involved in it

To determine the clock cycle time we need to consider the latencies of the components required for t... View full answer

Get step-by-step solutions from verified subject matter experts