Question: What is the critical path for an MIPS load (LD) instruction? Different execution units and blocks of digital logic have different latencies (time needed to

What is the critical path for an MIPS load (LD) instruction?

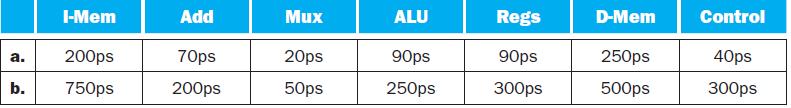

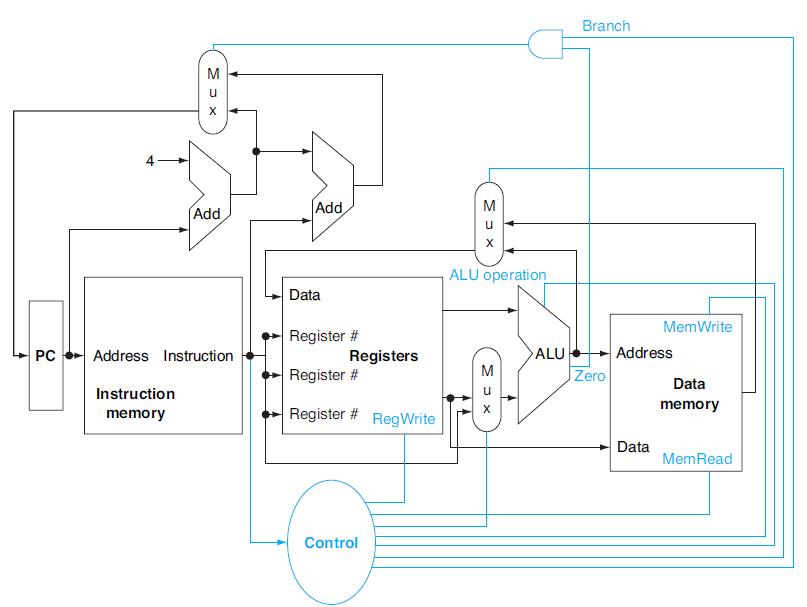

Different execution units and blocks of digital logic have different latencies (time needed to do their work). In Figure 4.2 there are seven kinds of major blocks. Latencies of blocks along the critical (longest-latency) path for an instruction determine the minimum latency of that instruction. For the remaining three problems in this exercise, assume the following resource latencies:

Figure 4.2

a. b. I-Mem 200ps 750ps Add 70ps 200ps Mux 20ps 50ps ALU 90ps 250ps Regs 90ps 300ps D-Mem 250ps 500ps Control 40ps 300ps

Step by Step Solution

3.42 Rating (149 Votes )

There are 3 Steps involved in it

An MIPS load LD instructions critical path can be found by determining the longestlatency path betwe... View full answer

Get step-by-step solutions from verified subject matter experts