Question: How many bits are there in the transmitter shift register of Fig. 11-8 when the interface is attached to a terminal that needs one stop

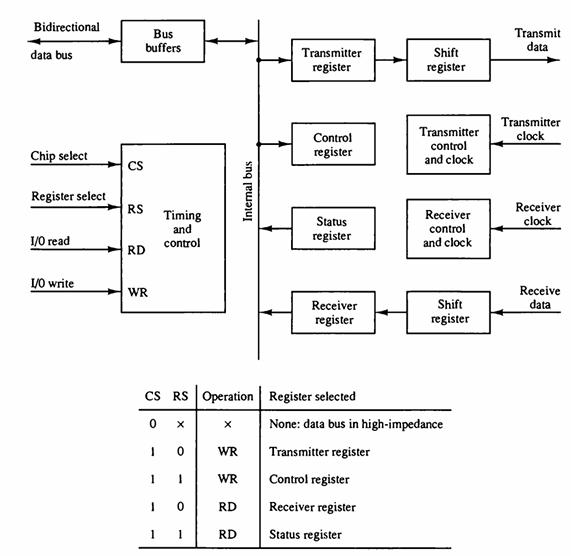

How many bits are there in the transmitter shift register of Fig. 11-8 when the interface is attached to a terminal that needs one stop bit? List the bits in the shift register when the letter W is transmitted using ASCII with even parity.

Fig. 11-8

Bidirectional data bus Chip select Register select 1/0 read I/O write Bus buffers CS RS RD WR 1 1 1 Timing and control 1 CS RS Operation Register selected 0 X 0 1 0 1 WR WR RD Internal bus RD Transmitter register Control register Status register Receiver register Shift register Control register Receiver register Status register Transmitter control and clock Receiver control and clock Shift register None: data bus in high-impedance Transmitter register Transmit data Transmitter clock Receiver clock Receive data

Step by Step Solution

3.42 Rating (146 Votes )

There are 3 Steps involved in it

The image provided shows a schematic diagram of a serial communication interface that includes a tra... View full answer

Get step-by-step solutions from verified subject matter experts