Question: You would like to use an FPGA to implement an M&M sorter with a color sensor and motors to put red candy in one jar

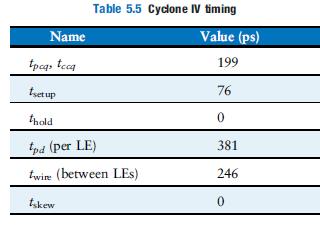

You would like to use an FPGA to implement an M&M sorter with a color sensor and motors to put red candy in one jar and green candy in another. The design is to be implemented as an FSM using a Cyclone IV FPGA. According to the data sheet, the FPGA has timing characteristics shown in Table 5.5. You would like your FSM to run at 100 MHz. What is the maximum number of LEs on the critical path? What is the fastest speed at which the FSM will run?

Table 5.5 Cydone IV timing Name Value (ps) tpegs tecq 199 tyetup 76 thold tpd (per LE) 381 twire (between LEs) 246 tskew

Step by Step Solution

3.26 Rating (161 Votes )

There are 3 Steps involved in it

With at most one LE on the cr... View full answer

Get step-by-step solutions from verified subject matter experts