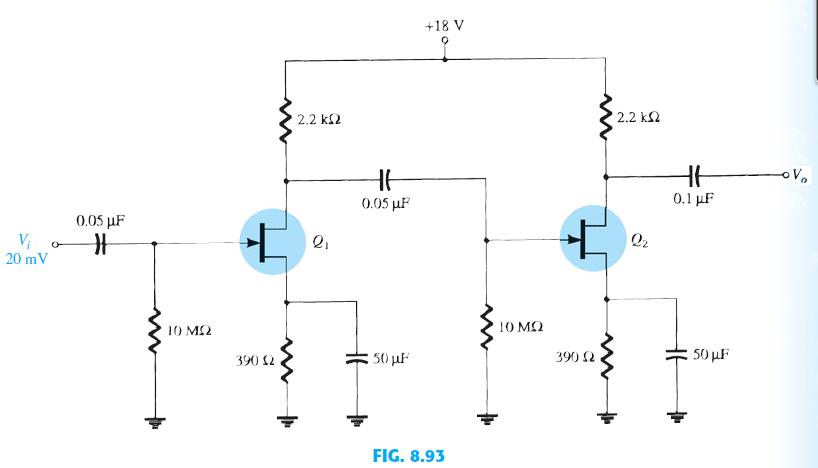

Use the Design Center to draw a schematic circuit of the cascade JFET amplifier as in Fig.8.93.

Question:

Use the Design Center to draw a schematic circuit of the cascade JFET amplifier as in Fig.8.93. Set the JFET parameters for IDSS = 12 mA and VP = 3V, and have the analysis determine the dc bias.

Fig.8.93

Transcribed Image Text:

+18 V 2.2 k2 2.2 k 0.05 µF 0.1 µF 0.05 µF 20 mV 10 M2 10 M2 390 2. 50 µF 50 µF 390 2 FIG. 8.93

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 73% (15 reviews)

Use the Design Center to draw a schematic circuit of the cascade ...View the full answer

Answered By

Labindao Antoque

I graduated in 2018 with a Bachelor of Science degree in Psychology from Dalubhasaan ng Lungsod ng San Pablo. I tutored students in classes and out of classes. I use a variety of strategies to tutor students that include: lecture, discussions about the subject matter, problem solving examples using the principles of the subject matter being discussed in class , homework assignments that are directed towards reinforcing what we learn in class , and detailed practice problems help students to master a concept. I also do thorough research on Internet resources or textbooks so that I know what students need to learn in order to master what is being taught in class .

0.00

0 Reviews

10+ Question Solved

Related Book For

Electronic Devices And Circuit Theory

ISBN: 9781292025636

11th Edition

Authors: Robert Boylestad, Louis Nashelsky

Question Posted:

Students also viewed these Engineering questions

-

Use the Design Center to draw a schematic circuit for a cascade JFET amplifier as shown in Fig. 8.93 . Set the analysis to calculate the ac output voltage V o for I DSS = 12 mA and V P = 3V. Fig....

-

Given IDSS = 12 mA and VP = 4 V, Draw the Drain characteristics for a p-JFET.

-

Fig. 18.43 shows a schematic circuit of an instrument called a potentiometer, which is a device for determining very accurate emf values of power supplies. It consists of three batteries, an ammeter,...

-

A posthole digger (the digger) is an agricultural implement manufactured by Alamo/SMC Corporation (SMC) designed, as its name implies, to dig holes in the ground for posts. The digger is...

-

State the law of supply. Why is price directly related to quantity supplied?

-

1. What perspective of organizational effectiveness did Tina Stavros and James Alder attempt to apply in this case? Describe how specific elements of that perspective related to their interventions....

-

a. Are the quadratic terms important? Consider a linear model of LNEXPENSES on 12 explanatory variables. For the explanatory variables, include assets, GROUP, both versions of losses and gross...

-

In the commercial production of sugar (sucrose), the product crystals are washed and centrifuged to partial dryness. The crystals are then sent through a rotary dryer where they are contacted with a...

-

How do mentorship frameworks accommodate the nuanced interplay of individual aspirations, cultural contexts, and socio-economic landscapes, facilitating the cultivation of diverse talent pools with...

-

You are CEO of Cactus Spine Medical Center in rural southeastern California. The 105-bed hospital has been operating in the same building since opening in 1957. In 2005, it undertook a $17,000,000...

-

Determine: a. 20 log 10 using Eq. (9.6) and compare with 20 log 10 14. b. 10 log 10 using Eq. (9.7) and compare with 10log 10 4 10 -3 . c. log 10 (40)(0.2) using Eq. (9.8) and compare with log10 8...

-

Using Multisim, determine the voltage gain for the network o Fig. 8.77. Fig. 8.77 +15 V 3.3 k2 Ipss = 8 mA Vp=-2.8 V ra= 40 k2 Zo 1.5 k2 FIG. 8.77

-

The FASB requires that a company organized in different operating segments disclose the revenues, profits, and assets of each of its major operating segments. Required Prepare a short memo that...

-

Mane Street normally sells 3000 economy-size bottles of shampoo for \(\$ 10\) per bottle. The cost to manufacture the shampoo is \(\$ 5.00\) per bottle. Further variable processing costs of \(\$...

-

The local council has been approached to set up a new industrial precinct of the edge of a suburb. A number of proposals have been put forward for the use of the land and the community has been...

-

A manufacturing business that makes photocopiers has annual net sales of \(\$ 30\) million from selling 60000 photocopiers per year. As a part of its manufacturing process, it consumes 150000...

-

The Possum Transport Company produces bikes, skates and mopeds. Mopeds are not as popular as they used to be, and the company is considering dropping this product. Possum currently sells 10000 mopeds...

-

An electronics manufacturing business is designing a new range of digital radios. The business is environmentally aware and has found a way to recycle old analogue radios as well as their new digital...

-

Identify A-L. (Hint: A shows three singlets in its spectrum with integral ratios and gives a positive iodoform test; see Section 19.4) HCl, H20 - CsH8O3 1. CH3O 2. CH2Br - excess HCI, H20 SOC2 2. H...

-

Using (1) or (2), find L(f) if f(t) if equals: t cos 4t

-

A solution of NaOH was standardized by titration of a known quantity of the primary standard, potassium hydrogen phthalate The NaOH was then used to find the concentration of an unknown solution of H...

-

Write the names and abbreviations for each of the prefixes from 10 -24 to 10 24 . Which abbreviations are capitalized?

-

What is the formal concentration (expressed as mol/L = M) of NaCl when 32.0 g are dissolved in water and diluted to 0.500 L?

-

1). The Electronic Corporation manufactures two electrical products: air conditioners and large fans. The assembly process for each is similar in that both require a certain amount of wiring and...

-

After reviewing oceanview marine company's case materials, and reviewing the unaudited account balances, what is your preliminary view on the client's ability to continue as a going concern? What is...

-

For each chemical reaction listed in the table below, decide whether the highlighted atom is being oxidized or reduced. reaction highlighted atom is being... neither oxidized reduced oxidized nor...

Study smarter with the SolutionInn App