Question: Consider the following Verilog statements (a)Write complete Verilog code to implement f1 and f2. (b) Use functional simulation to prove that f1 = f2. fl

Consider the following Verilog statements

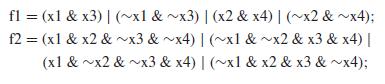

(a)Write complete Verilog code to implement f1 and f2.

(b) Use functional simulation to prove that f1 = f2.

fl = (x1 & x3)| (~x1 & ~x3) | (x2 & x4) | (~x2 & ~x4); f2 = (x1 & x2 & ~x3 & ~x4) | (~xl & ~x2 & x3 & x4) | (x1 & ~x2 & ~x3 & x4) | (~x1 & x2 & x3 & ~x4);

Step by Step Solution

3.46 Rating (159 Votes )

There are 3 Steps involved in it

a The first statement is an OR gate with four inputs The second statement is an OR gate with four in... View full answer

Get step-by-step solutions from verified subject matter experts