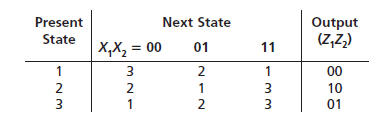

Question: Write Verilog code to implement the following state table. Use two always blocks. State changes should occur on the falling edge of the clock. Implement

Next State Present State Output (Z,Z,) 01 X,X, = 00 2 00 10 2 2 01

Step by Step Solution

3.41 Rating (164 Votes )

There are 3 Steps involved in it

module P54x1 x2 clk ... View full answer

Get step-by-step solutions from verified subject matter experts