Question: Create a Verilog module named h6to64 that represents a 6-to-64 binary decoder. Use the treelike structure in Figure 4.16, in which the 6-to-64 decoder is

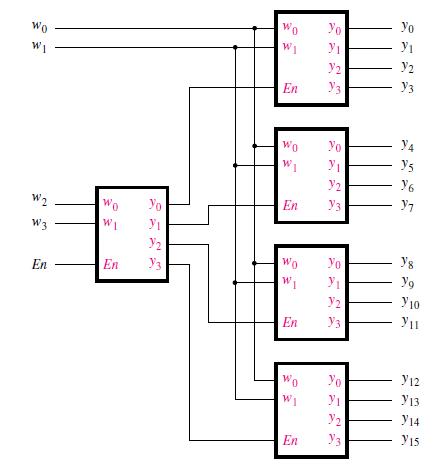

Create a Verilog module named h6to64 that represents a 6-to-64 binary decoder. Use the treelike structure in Figure 4.16, in which the 6-to-64 decoder is built using nine instances of the h3to8 decoder created in Problem 4.26.

Data From Problem 4.26

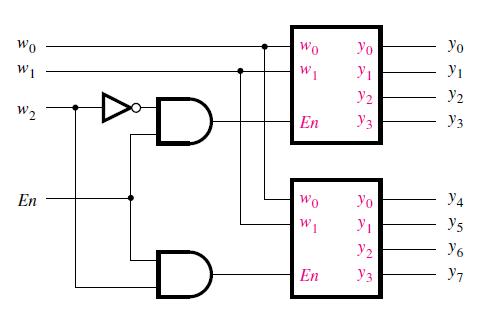

Create a Verilog module named if2to4 that represents a 2-to-4 binary decoder using an if-else statement. Create a second module named h3to8 that represents the 3-to-8 binary decoder in Figure 4.15 using two instances of the if2to4 module.

Wo WI W2 W3 En WO Yo Y 1/ En Y3 WI Wo 0 W En WO W Yo Y 2 En Y3 Wo W En WO W Yo Y1 V2 Y3 En Yo Y Y2 Y3 Yo Y 3/2 Y3 Yo Y1 Y2 Y3 Y4 Y5 36 97 Y8 Y9 10 YII Y12 Y13 Y14 Y15

Step by Step Solution

3.32 Rating (158 Votes )

There are 3 Steps involved in it

To create the 6to64 binary decoder module in Verilog we will first define the 2to4 and 3to8 decoders as per the information provided in Problem 426 an... View full answer

Get step-by-step solutions from verified subject matter experts