Question: In Example 9.21 we designed a circuit that replicates every second pulse on input w as a pulse on output z. Design a similar circuit

In Example 9.21 we designed a circuit that replicates every second pulse on input w as a pulse on output z. Design a similar circuit that replicates every third pulse.

Example 9.21

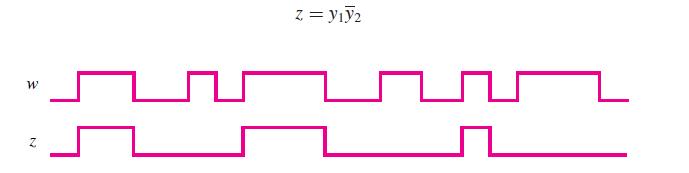

Problem: A circuit has an input w and an output z. A sequence of pulses is applied on input w. The output has to replicate every second pulse, as illustrated in Figure 9.79. Design a suitable circuit.

Compare this with the FSM defined in Example 9.4 in Figure 9.13, which specifies a serial parity generator. The only difference is in the output signal. In our case, z = 1 only in state B. Therefore, the next-state expressions are the same as in Example 9.4. The output expression is

W N 2 = V12

Step by Step Solution

3.36 Rating (174 Votes )

There are 3 Steps involved in it

The design of a circuit that replicates every third pulse can be achieved by modifying t... View full answer

Get step-by-step solutions from verified subject matter experts