Question: Write Verilog code for the FSM designed in Problem 6.37. Data From Problem 6.37 The arbiter FSM defined in Section 6.8 (Figure 6.72) may cause

Write Verilog code for the FSM designed in Problem 6.37.

Data From Problem 6.37

The arbiter FSM defined in Section 6.8 (Figure 6.72) may cause device 3 to never get serviced if devices 1 and 2 continuously keep raising requests, so that in the Idle state it always happens that either device 1 or device 2 has an outstanding request. Modify the proposed FSM to ensure that device 3 will get serviced, such that if it raises a request, the devices 1 and 2 will be serviced only once before the device 3 is granted its request.

Data From Section6.8

FSM as an Arbiter Circuit

In this section we present the design of an FSM that is slightly more complex than the previous examples. The purpose of the machine is to control access by various devices to a shared resource in a given system. Only one device can use the resource at a time. Assume that all signals in the system can change values only following the positive edge of the clock signal. Each device provides one input to the FSM, called a request, and the FSM produces a separate output for each device, called a grant. Adevice indicates its need to use the resource by asserting its request signal. Whenever the shared resource is not already in use, the FSM considers all requests that are active. Based on a priority scheme, it selects one of the requesting devices and asserts its grant signal. When the device is finished using the resource, it deasserts its request signal.

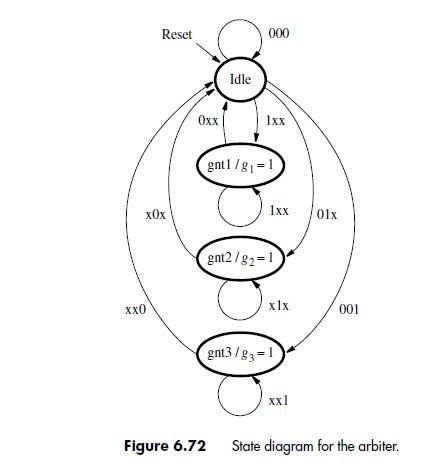

We will assume that there are three devices in the system, called device 1, device 2, and device 3. It is easy to see how the FSM can be extended to handle more devices. The request signals are named 7, 72, and r3, and the grant signals are called g, g2, and g3. The devices are assigned a priority level such that device 1 has the highest priority, device 2 has the next highest, and device 3 has the lowest priority. Thus if more than one request signal is asserted when the FSM assigns a grant, the grant is given to the requesting device that has the highest priority. A state diagram for the desired FSM, designed as a Moore-type machine, is depicted in Figure 6.72. Initially, on reset the machine is in the state called Idle. No grant signals are asserted, and the shared resource is not in use. There are three other states, called gntl, gnt2, and gnt3. Each of these states asserts the grant signal for one of the devices. The FSM remains in the Idle state as long as all of the request signals are 0. In the state diagram the condition 1273 = 000 is indicated by the arc labeled 000. When one or more request signals become 1, the machine moves to one of the grant states, according to the priority scheme. If r is asserted, then device 1 will receive the grant because it has the highest priority. This is indicated by the arc labeled 1xx that leads to state gntl, which sets g = 1. The meaning of 1xx is that the request signal r is 1, and the values of signals

Step by Step Solution

3.28 Rating (169 Votes )

There are 3 Steps involved in it

To modify the given arbiter FSM to ensure that device 3 gets serviced even if devices 1 and 2 contin... View full answer

Get step-by-step solutions from verified subject matter experts