Question: Generate a verification sequence for the circuit described by the state table in Table 4-14. To reduce the length of the simulation sequence, assume that

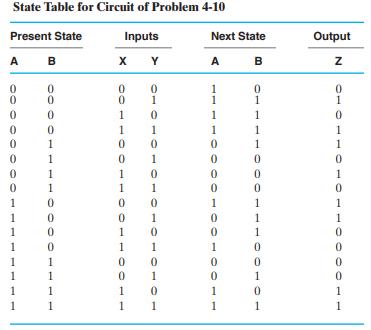

Generate a verification sequence for the circuit described by the state table in Table 4-14. To reduce the length of the simulation sequence, assume that the simulator can handle X inputs and use X’s whenever possible. Assume that a Reset input is available to initialize the state to A = 0, B = 0 and that all transitions in the state diagram must be exercised.

Table 4-14:

State Table for Circuit of Problem 4-10 Present State Inputs Y A B 00000 0 0 0 1 1 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 X 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Next State B A 1 1 1 0 0 1100TOOT00 0 1 1 1 1 0 0 0 1 1 1 0 0 1 0 1 Output N 0 1 0 1 1 0 1 0 1 1 0 0 0 0 1 1

Step by Step Solution

3.44 Rating (157 Votes )

There are 3 Steps involved in it

Based on the image you provided Table 414 describes a sequential circuit with two state bits A and B two input signals X and Y one output signal Z and ... View full answer

Get step-by-step solutions from verified subject matter experts