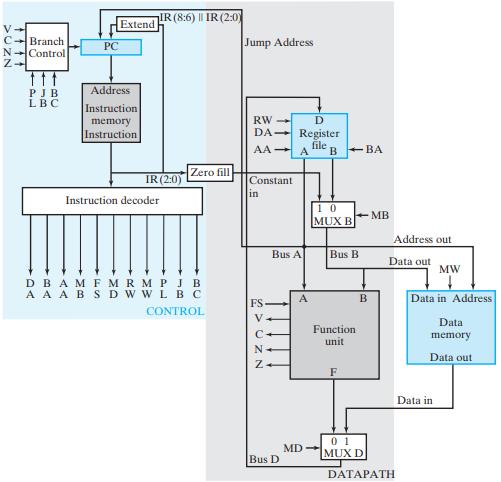

The single- cycle computer in Figure 8-15 executes the ive instructions described by the register transfers in

Question:

The single- cycle computer in Figure 8-15 executes the ive instructions described by the register transfers in the table that follows.

Figure 8-15

(a) Complete the following table, giving the binary instruction decoder outputs from Figure 8-16 during execution of each of the instructions:

![Instruction Register Transfer R[0] R[7] R[3] R[1] M[R[4]] R[2] R[5]+2 R[3] sl R[6] if (R([4] = 0) PC](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1704/5/6/8/2286599a5a42333e1704568225237.jpg)

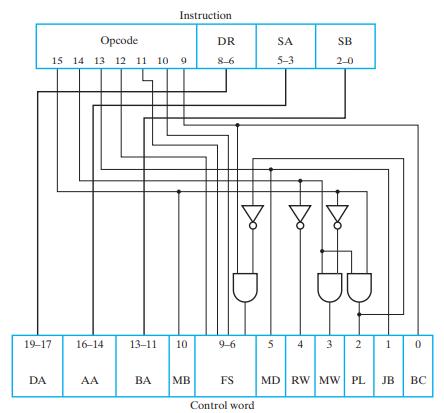

Figure 8-16

(b) Complete the following table, giving the instruction in binary for the single-cycle computer that executes the register transfer (if any field is not used, give it the value 0):

![Instruction Register Transfer R[0] R[7]+R[6] R[1] R[5]-1 R[2] sl R[4] R[3] R[3] R[4] R[2] V R[1] Opcode](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1704/5/6/8/3026599a5ee6a6b21704568300505.jpg)

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Logic And Computer Design Fundamentals

ISBN: 9780133760637

5th Edition

Authors: M. Morris Mano, Charles Kime, Tom Martin

Question Posted: