Question: Assume that the delay in a delay-and-multiply receiver for DPSK as shown in Fig. 9.17 is in error by |ÎT|. (a) Show that the asymptotic

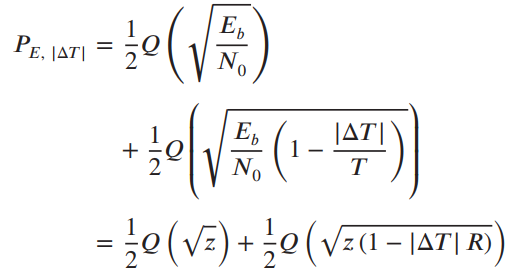

(a) Show that the asymptotic bit error probability becomes

(Consider the possible data sequences 11, 00, 10, and 01 thereby accounting for the cases of degradation and no degradation in the signal component at the integrator output.)

(b) Plot PE,|ΔT| versus z in dB for |Δf| R = 0, 0.1, 0.2, 0.3, 0.4. Estimate the degradation in dB at a probability of error of 10-6.

E, PE, IAT| N JAT| Ep No = e(VE) + e(vz(1 |AT| R)

Step by Step Solution

3.44 Rating (170 Votes )

There are 3 Steps involved in it

a By plotting sequences of two successive bit wave forms it is seen that no energy cancellatio... View full answer

Get step-by-step solutions from verified subject matter experts