Question: 0 Create a 3 bit ripple using the structural approach of instantiation in verilog and do not vectorize inputs to your module, call this module

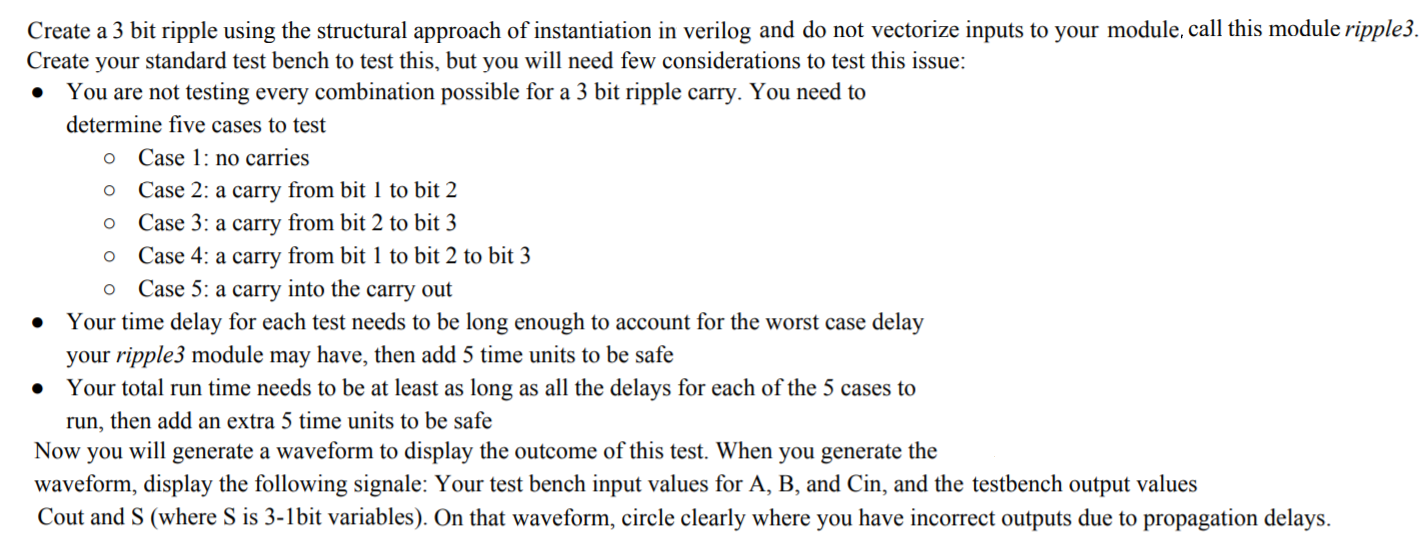

0 Create a 3 bit ripple using the structural approach of instantiation in verilog and do not vectorize inputs to your module, call this module ripple3. Create your standard test bench to test this, but you will need few considerations to test this issue: You are not testing every combination possible for a 3 bit ripple carry. You need to determine five cases to test o Case 1: no carries o Case 2: a carry from bit 1 to bit 2 Case 3: a carry from bit 2 to bit 3 o Case 4: a carry from bit 1 to bit 2 to bit 3 o Case 5: a carry into the carry out Your time delay for each test needs to be long enough to account for the worst case delay your ripple3 module may have, then add 5 time units to be safe Your total run time needs to be at least as long as all the delays for each of the 5 cases to run, then add an extra 5 time units to be safe Now you will generate a waveform to display the outcome of this test. When you generate the waveform, display the following signale: Your test bench input values for A, B, and Cin, and the testbench output values Cout and S (where S is 3-1 bit variables). On that waveform, circle clearly where you have incorrect outputs due to propagation delays. 0 Create a 3 bit ripple using the structural approach of instantiation in verilog and do not vectorize inputs to your module, call this module ripple3. Create your standard test bench to test this, but you will need few considerations to test this issue: You are not testing every combination possible for a 3 bit ripple carry. You need to determine five cases to test o Case 1: no carries o Case 2: a carry from bit 1 to bit 2 Case 3: a carry from bit 2 to bit 3 o Case 4: a carry from bit 1 to bit 2 to bit 3 o Case 5: a carry into the carry out Your time delay for each test needs to be long enough to account for the worst case delay your ripple3 module may have, then add 5 time units to be safe Your total run time needs to be at least as long as all the delays for each of the 5 cases to run, then add an extra 5 time units to be safe Now you will generate a waveform to display the outcome of this test. When you generate the waveform, display the following signale: Your test bench input values for A, B, and Cin, and the testbench output values Cout and S (where S is 3-1 bit variables). On that waveform, circle clearly where you have incorrect outputs due to propagation delays

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts