Question: 0 Points) Assume a 5 stage processor like the one discussed in class and the text. Answer the following questions assuming the 5 stages have

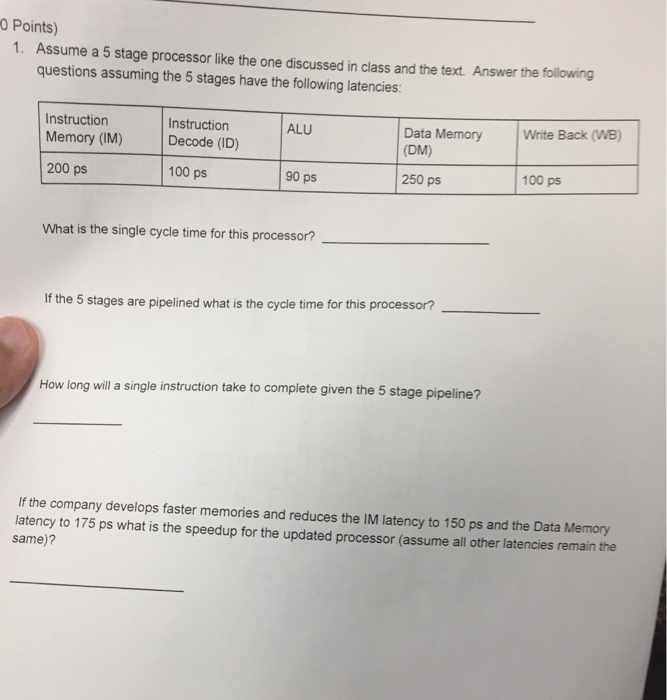

0 Points) Assume a 5 stage processor like the one discussed in class and the text. Answer the following questions assuming the 5 stages have the following latencies 1. Data Memory Write Back (WB) (DM) Instruction ALU Instruction Memory (IM) Decode (ID) 200 ps 100 ps 100 ps 90 ps 250 ps What is the single cycle time for this processor? If the 5 stages are pipelined what is the cycle time for this processor? How long will a single instruction take to complete given the 5 stage pipeline? If the company develops faster memories and reduces the IM latency to 150 ps and the Data Memory latency to 175 ps what is the speedup for the updated processor (assume all other latencies remain the same)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts