Question: 1. (25 pts.) A hypothetical cache memory has 64 bytes of storage. Assume the memory is byte addressable and the following sequence of address references

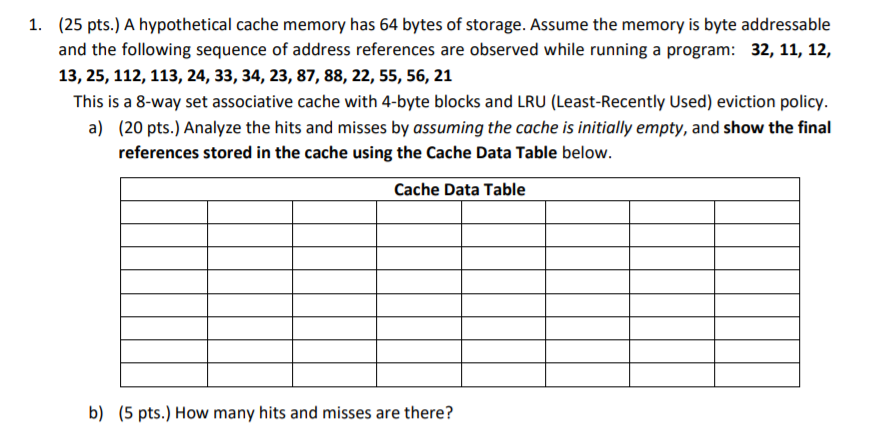

1. (25 pts.) A hypothetical cache memory has 64 bytes of storage. Assume the memory is byte addressable and the following sequence of address references are observed while running a program: 32, 11, 12, 13, 25, 112, 113, 24, 33, 34, 23, 87, 88, 22, 55, 56, 21 This is a 8-way set associative cache with 4-byte blocks and LRU (Least-Recently Used) eviction policy. a) (20 pts.) Analyze the hits and misses by assuming the cache is initially empty, and show the final references stored in the cache using the Cache Data Table below. Cache Data Table b) (5 pts.) How many hits and misses are there

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts