Question: 1. (50 points) The following instructions are executed on the 5-stage MIPS pipelined datapath add r5,r2, r1 lw r3, 4(r5) lw r2, 0(r2) or r3,

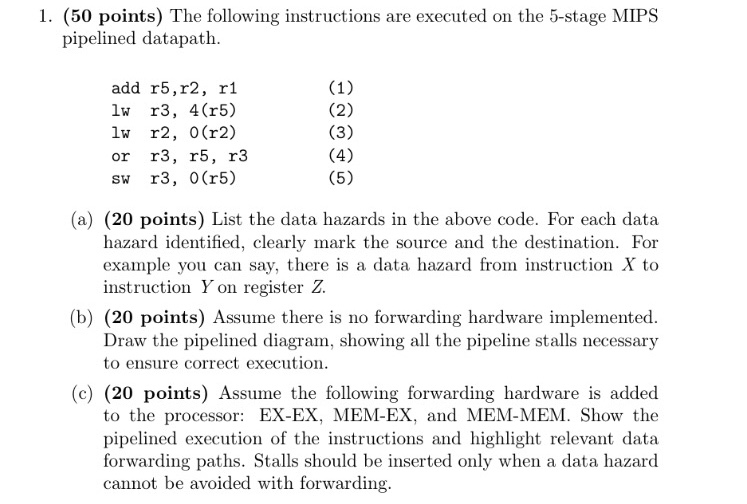

1. (50 points) The following instructions are executed on the 5-stage MIPS pipelined datapath add r5,r2, r1 lw r3, 4(r5) lw r2, 0(r2) or r3, r5, r: sw r3, 0(r5) (a) (20 points) List the data hazards in the above code. For each data hazard identified, clearly mark the source and the destination. For example you can say, there is a data hazard from instruction X to instruction Y on register Z. (b) (20 points) Assume there is no forwarding hardware implemented Draw the pipelined diagram, showing all the pipeline stalls necessary to ensure correct execution (c) (20 points) Assume the following forwarding hardware is added to the processor: EX-EX, MEM-EX, and MEM-MEM. Show the pipelined execution of the instructions and highlight relevant data forwarding paths. Stalls should be inserted only when a data hazard cannot be avoided with forwarding

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts