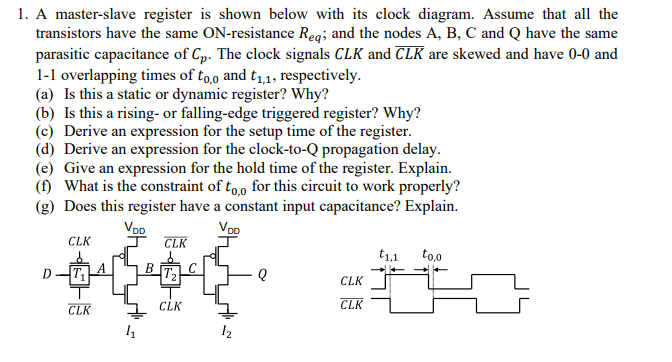

Question: 1 . A master - slave register is shown below with its clock diagram. Assume that all the transistors have the same ON - resistance

A masterslave register is shown below with its clock diagram. Assume that all the transistors have the same ONresistance Re q; and the nodes mathrmAmathrmBmathrmC and Q have the same parasitic capacitance of Cp The clock signals C L K and overlineC L K are skewed and have and overlapping times of t and t respectively.

a Is this a static or dynamic register? Why?

b Is this a rising or fallingedge triggered register? Why?

c Derive an expression for the setup time of the register.

d Derive an expression for the clocktoQ propagation delay.

e Give an expression for the hold time of the register. Explain.

f What is the constraint of t for this circuit to work properly?

g Does this register have a constant input capacitance? Explain.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock