Question: 1. A synchronous finite state machine has a single 'Serial Data' input (SD) and a single output (T). The output changes on the rising edge

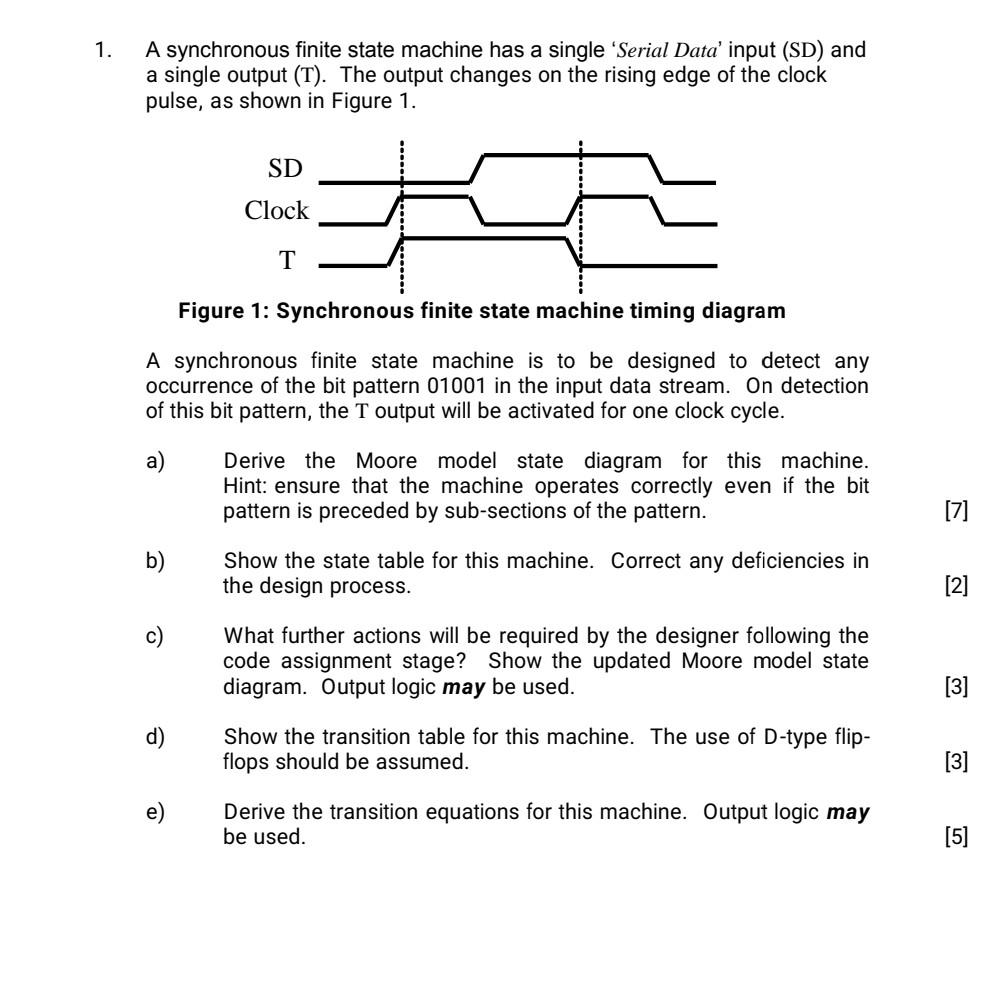

1. A synchronous finite state machine has a single 'Serial Data' input (SD) and a single output (T). The output changes on the rising edge of the clock pulse, as shown in Figure 1. SD Clock T Figure 1: Synchronous finite state machine timing diagram A synchronous finite state machine is to be designed to detect any occurrence of the bit pattern 01001 in the input data stream. On detection of this bit pattern, the T output will be activated for one clock cycle. a) Derive the Moore model state diagram for this machine. Hint: ensure that the machine operates correctly even if the bit pattern is preceded by sub-sections of the pattern. [7] b) Show the state table for this machine. Correct any deficiencies in the design process. [2] What further actions will be required by the designer following the code assignment stage? Show the updated Moore model state diagram. Output logic may be used. [3] d) Show the transition table for this machine. The use of D-type flip- flops should be assumed. [3] Derive the transition equations for this machine. Output logic may be used. [5]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts