Question: ( # 1 ) Combinational Circuit design, synthesis and simulation For the XOR gate shown, Code for 3 levels of the design: Gate, RTL ,

# Combinational Circuit design, synthesis and simulation

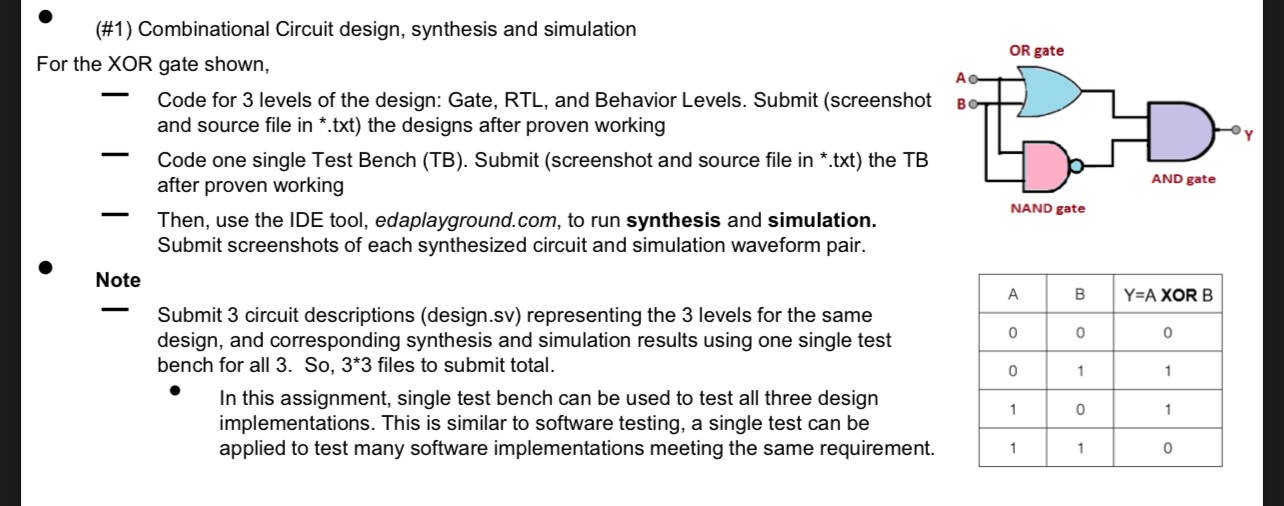

For the XOR gate shown,

Code for levels of the design: Gate, RTL and Behavior Levels. Submit screenshot and source file in txt the designs after proven working

Code one single Test Bench TB Submit screenshot and source file in txt the TB after proven working

Then, use the IDE tool,

edaplayground.com, to run synthesis and simulation. Submit screenshots of each synthesized circuit and simulation waveform pair.

Note

Submit circuit descriptions

design.sv representing the levels for the same design, and corresponding synthesis and simulation results using one single test bench for all So files to submit total.

In this assignment, single test bench can be used to test all three design implementations. This is similar to software testing, a single test can be applied to test many software implementations meeting the same requirement.

tableA XOR B

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock