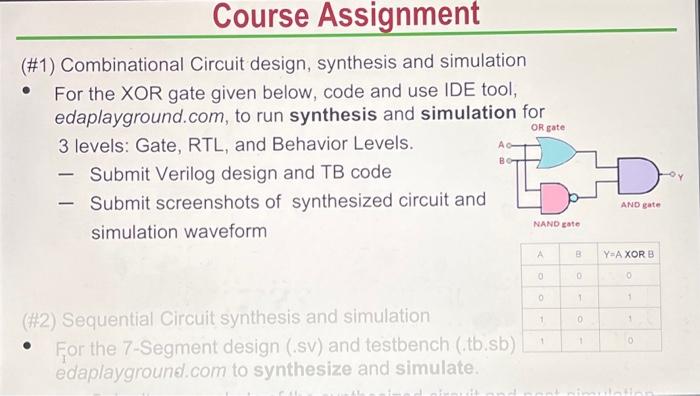

Question: (#1) Combinational Circuit design, synthesis and simulation - For the XOR gate given below, code and use IDE tool, edaplayground.com, to run synthesis and simulation

(\#1) Combinational Circuit design, synthesis and simulation - For the XOR gate given below, code and use IDE tool, edaplayground.com, to run synthesis and simulation for 3 levels: Gate, RTL, and Behavior Levels. - Submit Verilog design and TB code - Submit screenshots of synthesized circuit and simulation waveform (\#2) Sequential Circuit synthesis and simulation - For the 7-Segment design (.sv) and testbench (.tb.sb) edaplayground.com to synthesize and simulate. Lob3.0 Verilos. Smothosis and Simulation [591.pdt 1. While you need to submit 3 circuit representations representing the 3- levels For the same design, you only need to demanatrate writhesis and umulaban on ane of the implementation using a lest bench. 2. In this assignment, single test bench can be used to test all three design implementations. This is simdar to software testing, a sirgle test can be appled to lest many sofware implamentatons of the same requirement. 3. The Assignment page in the stide deck has two cases. - iTXOR. - m2 7-Segment. You only need to do $1. (it2 is taded, no need to work on 42 .)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts