Question: 1 CPU Datapath The following figure shows the overall data path of the simple 5 - stage CPU we have learned. There are four multiplexers

CPU Datapath

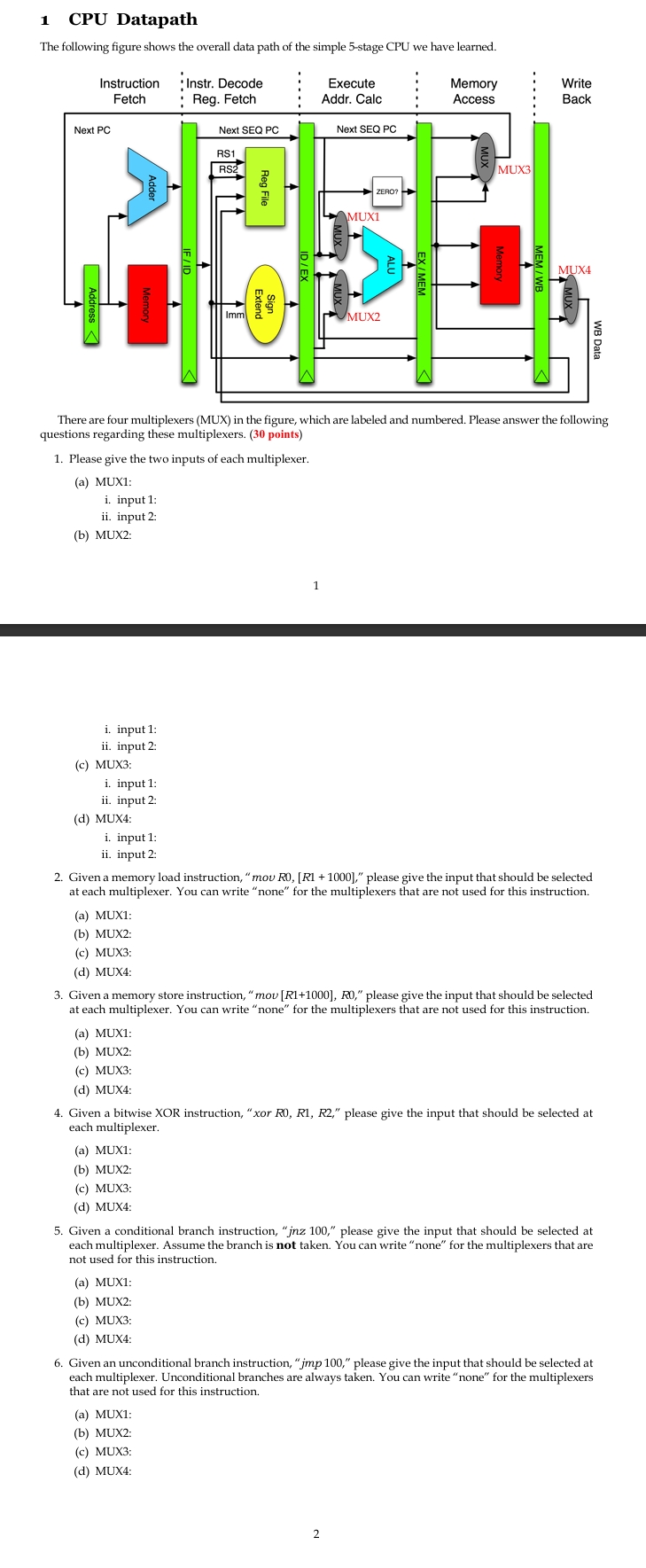

The following figure shows the overall data path of the simple stage CPU we have learned.

There are four multiplexers MUX in the figure, which are labeled and numbered. Please answer the following questions regarding these multiplexers. points

Please give the two inputs of each multiplexer.

a MUX:

i input :

ii input :

b MUX:

i input :

ii input :

c MUX:

i input :

ii input :

d MUX:

i input :

ii input :

Given a memory load instruction, "mov R R please give the input that should be selected at each multiplexer. You can write "none" for the multiplexers that are not used for this instruction.

a MUX:

b MUX:

c MUX:

d MUX:

Given a memory store instruction, mathrmmovR R please give the input that should be selected at each multiplexer. You can write "none" for the multiplexers that are not used for this instruction.

a MUX:

b MUX:

c MUX:

d MUX:

Given a bitwise XOR instruction, xor R R R please give the input that should be selected at each multiplexer.

a MUX:

b MUX:

c MUX:

d MUX:

Given a conditional branch instruction, jnz please give the input that should be selected at each multiplexer. Assume the branch is not taken. You can write "none" for the multiplexers that are not used for this instruction.

a MUX:

b MUX:

c MUX:

d MUX:

Given an unconditional branch instruction, jmp please give the input that should be selected at each multiplexer. Unconditional branches are always taken. You can write "none" for the multiplexers that are not used for this instruction.

a MUX:

b MUX:

c MUX:

d MUX:

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock