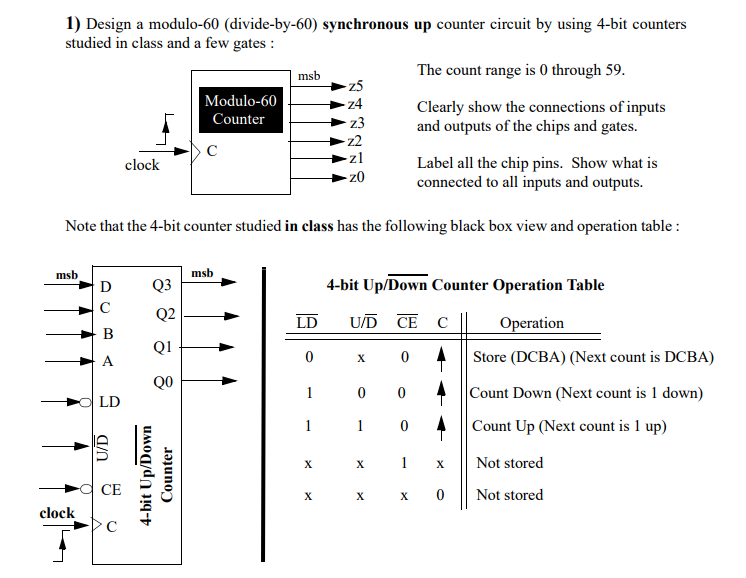

Question: 1) Design a modulo-60 (divide-by-60) synchronous up counter circuit by using 4-bit counters studied in class and a few gates: The count range is 0

1) Design a modulo-60 (divide-by-60) synchronous up counter circuit by using 4-bit counters studied in class and a few gates: The count range is 0 through 59 Modulo-60 Counter 24 Clearly show the connections of inputs and outputs of the chips and gates. z2 Label all the chip pins. Show what is connected to all inputs and outputs. cloc Note that the 4-bit counter studied in class has the following black box view and operation table msb msb D Q3 4-bit Up/Down Counter Operation Table LD U/D CE C ation Q1 Store (DCBA) (Next count is DCBA) Count Down (Next count is 1 down) Count Up (Next count is 1 up) LD x1 xNot stored CE x x 0Not stored clock

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock