Question: 1. For the below synchronous sequential circuit assume maximum and minimum clock-to- output delay for flip-flops are 15ms and 5ms, respectively. Delay for gates are

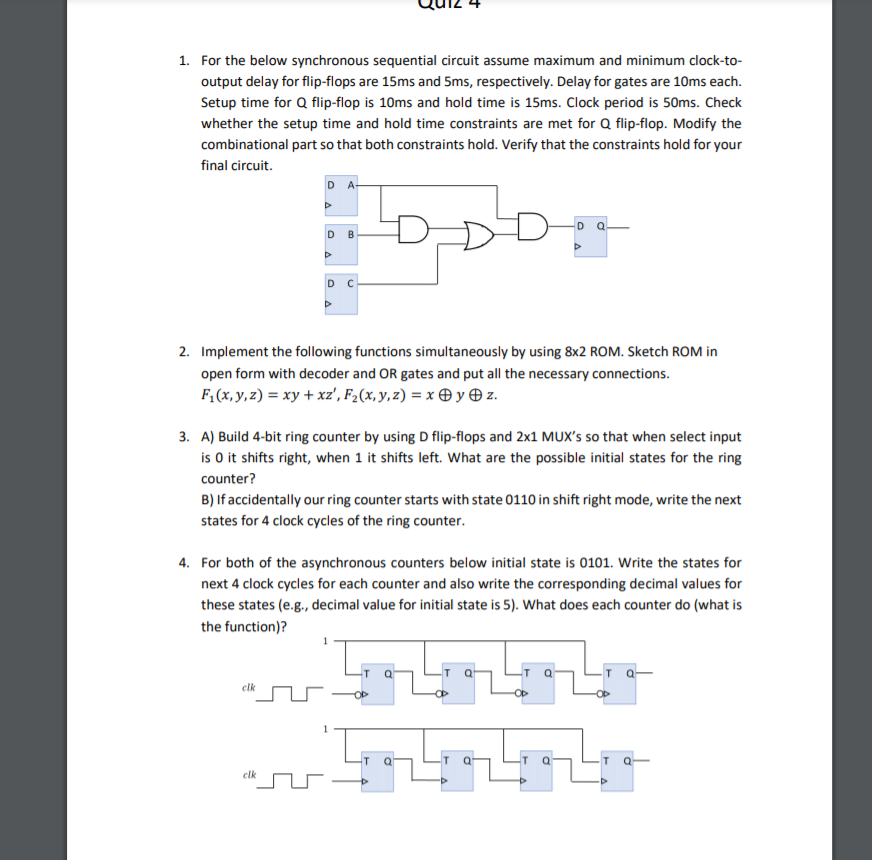

1. For the below synchronous sequential circuit assume maximum and minimum clock-to- output delay for flip-flops are 15ms and 5ms, respectively. Delay for gates are 10ms each. Setup time for Q flip-flop is 10ms and hold time is 15ms. Clock period is 50ms. Check whether the setup time and hold time constraints are met for Q flip-flop. Modify the combinational part so that both constraints hold. Verify that the constraints hold for your final circuit. D A D D Q D B D C 2. Implement the following functions simultaneously by using 8x2 ROM. Sketch ROM in open form with decoder and OR gates and put all the necessary connections. F2(x, y, z) = xy + xz',F2(x,y,z) = xyz. 3. A) Build 4-bit ring counter by using D flip-flops and 2x1 MUX's so that when select input is 0 it shifts right, when 1 it shifts left. What are the possible initial states for the ring counter? B) If accidentally our ring counter starts with state 0110 in shift right mode, write the next states for 4 clock cycles of the ring counter. 4. For both of the asynchronous counters below initial state is 0101. Write the states for next 4 clock cycles for each counter and also write the corresponding decimal values for these states (e.g., decimal value for initial state is 5). What does each counter do (what is the function)? clk OP 1752 clk

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts