Question: Below is a sequential circuit consisting of two D Flip-Flops and a combinational logic network which produces the D inputs to the Flip-Flops as well

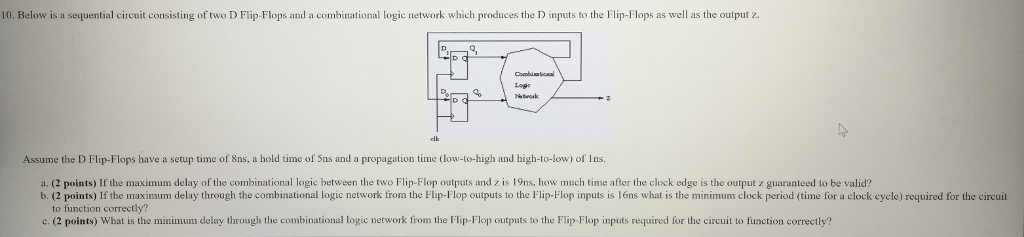

Below is a sequential circuit consisting of two D Flip-Flops and a combinational logic network which produces the D inputs to the Flip-Flops as well as the output z. Assume the D Flip-Flops have a setup time of 8ns, a hold time of 5ns and a propagation time (low-to-high and high-to-low) of Ins. a. If the maximum delay of the combinational logic between the two Flip-Flop outputs and z is 19ns, how much time after the clock edge is the output z guaranteed to be valid? b. If the maximum delay through the combinational logic network from the Flip-Flop outputs to the Flip-Flop inputs is 16ns what is the minimum clock period (time for a clock cycle) required for the circuit to function correctly? c. What is the minimum delay through the combinational logic network from the Flip-Flop outputs to the Flip-Flop inputs required for the circuit to function correctly

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts