Question: 1 Problem A processor takes one clock cycle to execute each instruction, when no memory stalls are present. Its level 1 cache has a miss

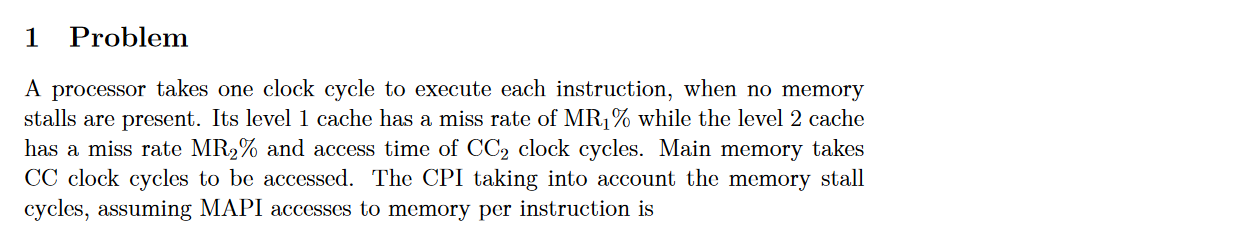

1 Problem A processor takes one clock cycle to execute each instruction, when no memory stalls are present. Its level 1 cache has a miss rate of MR % while the level 2 cache has a miss rate MR2% and access time of CC2 clock cycles. Main memory takes CC clock cycles to be accessed. The CPI taking into account the memory stall cycles, assuming MAPI accesses to memory per instruction is

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts