Question: 1. Ripple-Carry Adder RCA) First write a module for a full adder (FA) with: Inputs: x, y and cin (all 1 bit). outputs: s and

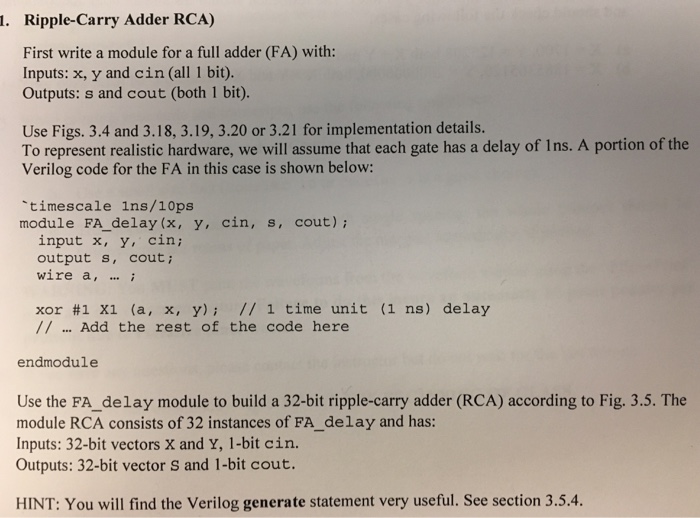

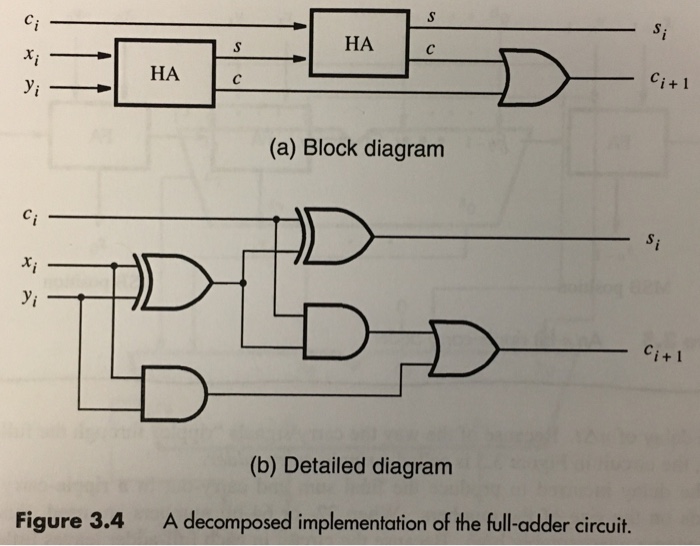

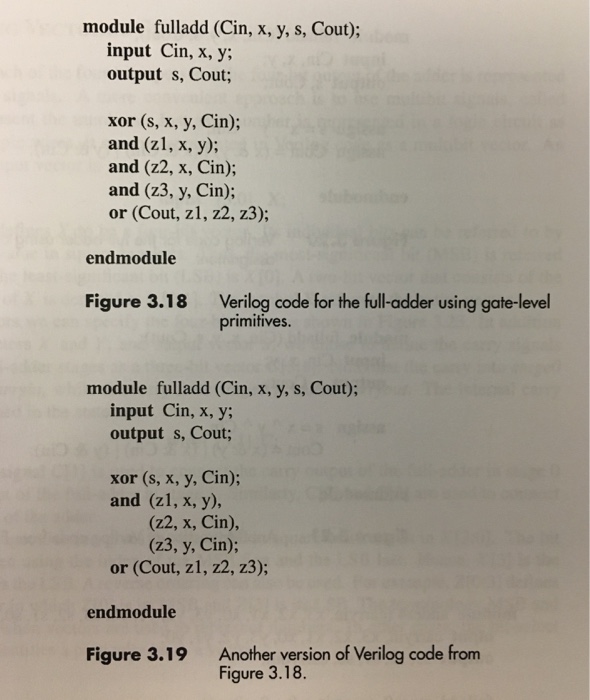

1. Ripple-Carry Adder RCA) First write a module for a full adder (FA) with: Inputs: x, y and cin (all 1 bit). outputs: s and cout (both 1 bit). Use Figs. 3.4 and 3.18, 3.19, 3.20 or 3.21 for implementation details. To represent realistic hardware, we will assume that each gate has a delay of 1ns. A portion of the Verilog code for the FA in this case is shown below: timescale 1ns/10ps module FA delay (x, y, cin, s, cout) input x, y, cin output s Cout wire a xor #1 X1 (a, x, y) 1 time unit (1 ns) delay Add the rest of the code here endmodule Use the FA delay module to build a 32-bit ripple-carry adder (RCA) according to Fig. 3.5. The module RCA consists of 32 instances of FA delay and has Inputs: 32-bit vectors x and Y, 1-bit cin. Outputs: 32-bit vector s and 1-bit cout. HINT: You will find the Verilog generate statement very useful. See section 3.5.4

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts