Question: 1. Schedule the following code using Tomasulo's algorithm assuming the hardware has the following architecture: . . 3 load units with 2 cycles execution latency

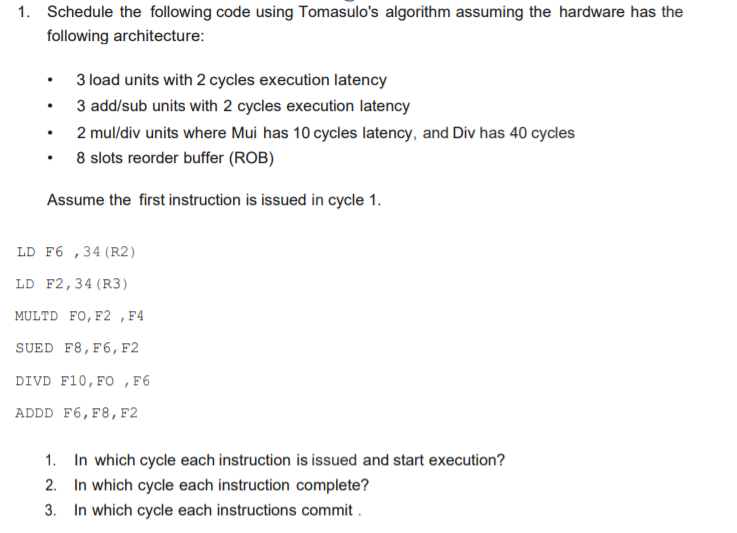

1. Schedule the following code using Tomasulo's algorithm assuming the hardware has the following architecture: . . 3 load units with 2 cycles execution latency 3 add/sub units with 2 cycles execution latency 2 mul/div units where Mui has 10 cycles latency, and Div has 40 cycles 8 slots reorder buffer (ROB) Assume the first instruction is issued in cycle 1. LD F6,34 (R2) LD F2,34 (R3) MULTD FO, F2, F4 SUED F8, F6, F2 DIVD F10, FO ,F6 ADDD F6, F8, F2 1. In which cycle each instruction is issued and start execution? 2. In which cycle each instruction complete? 3. In which cycle each instructions commit. 1. Schedule the following code using Tomasulo's algorithm assuming the hardware has the following architecture: . . 3 load units with 2 cycles execution latency 3 add/sub units with 2 cycles execution latency 2 mul/div units where Mui has 10 cycles latency, and Div has 40 cycles 8 slots reorder buffer (ROB) Assume the first instruction is issued in cycle 1. LD F6,34 (R2) LD F2,34 (R3) MULTD FO, F2, F4 SUED F8, F6, F2 DIVD F10, FO ,F6 ADDD F6, F8, F2 1. In which cycle each instruction is issued and start execution? 2. In which cycle each instruction complete? 3. In which cycle each instructions commit

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts