Question: 1. Use Karnaugh Maps to implement and minimize below truth tables. Implement the minimized function using only 2-input AND gates, 2-input OR gates and 1-input

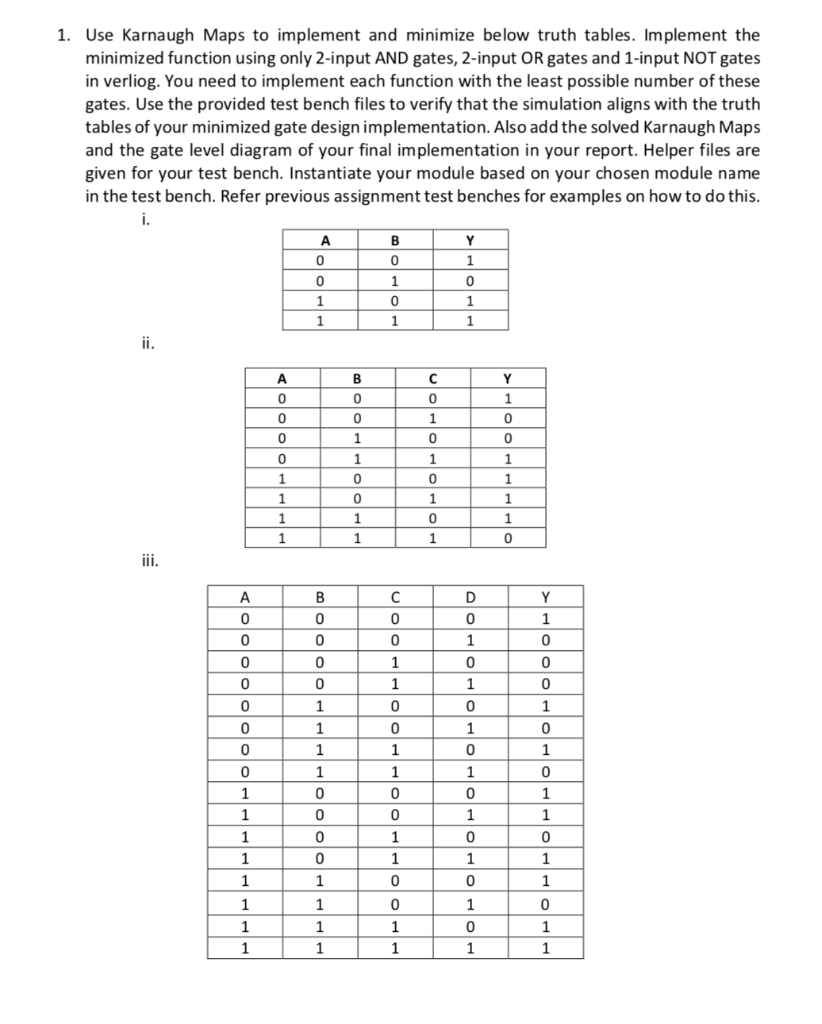

1. Use Karnaugh Maps to implement and minimize below truth tables. Implement the minimized function using only 2-input AND gates, 2-input OR gates and 1-input NOT gates in verliog. You need to implement each function with the least possible number of these gates. Use the provided test bench files to verify that the simulation aligns with the truth tables of your minimized gate design implementation. Also add the solved Karnaugh Maps and the gate level diagram of your final implementation in your report. Helper files are given for your test bench. Instantiate your module based on your chosen module name in the test bench. Refer previous assignment test benches for examples on how to do this. B 0 0 0 1 1 Y 1 0 1 1 0 1 1 ii. A B Y 1 0 0 0 1 0 0 0 0 0 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 1 1 1 0 1 1 1 iii. A D Y B 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 1 1 0 0 1 0 0 1 1 1 1 0 0 1 0 1 1 0 1 0 1 0 0 1 0 0 1 0 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 0 1 0 1 0 1 1 1 0 0 1 1 0 1 1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts