Question: 18. Design a D flip-flop circuit with asynchronous Clear (CLR) using NAND gates. The flip-flop should: Set its Q output to 1 when D=1 on

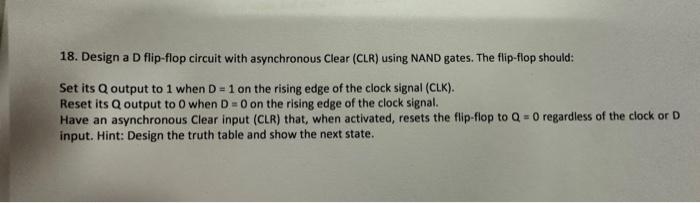

18. Design a D flip-flop circuit with asynchronous Clear (CLR) using NAND gates. The flip-flop should: Set its Q output to 1 when D=1 on the rising edge of the clock signal (CLK). Reset its Q output to 0 when D=0 on the rising edge of the clock signal. Have an asynchronous Clear input (CLR) that, when activated, resets the flip-flop to Q=0 regardless of the clock or D input. Hint: Design the truth table and show the next state

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts