Question: 1.For the MIPS instruction sequence below, complete the data dependency diagram. (Destination register is listed first except for sw instruction; sw writes into memory rather

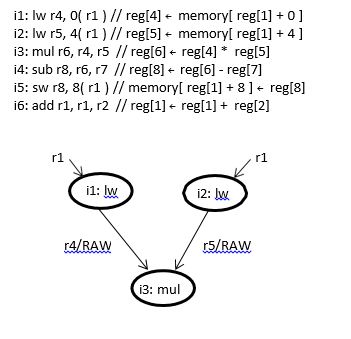

1.For the MIPS instruction sequence below, complete the data dependency diagram. (Destination register is listed first except for sw instruction; sw writes into memory rather than a register.)

il: lw r4, 0( r1 ) // reg[4] memoryl reg[1] + 0 ] i2: lw r5, 4( r1 ) // reg[5] memoryl reg[1] + 4 ] 13: mul r6, r4, r5 // reg[6] reg[4] * reg[5] A: sub r8, r6, r7 // reg[8] reg[6]-reg[7] 15. Sw r8, 8( r1 ) // memory[ reg[1] + 8 ] reg[8] i6: add r1, r1, r2 // reg[1] reg[1] + reg[2] rl rl 4 RAW 5/RAW i3: mul

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts