Question: 1.Use structural coding style to implement the following design in VHDL 2. Design a MUX-DEMUX with registered outputs: Design will have a 4-to-1 MUX followed

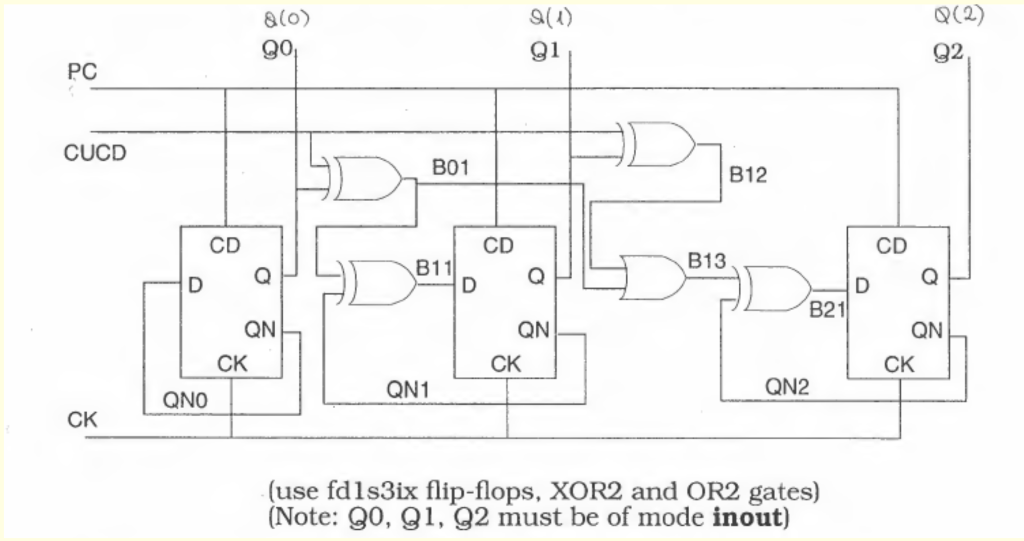

1.Use structural coding style to implement the following design in VHDL

2. Design a MUX-DEMUX with registered outputs:

Design will have a 4-to-1 MUX followed by a 1-to-8 DEMUX.

Use flip-flops for DEMUX outputs by instantiating DFF as in COMPONENT DFF IS

PORT( D : IN STD_LOGIC;

CLOCK : IN STD_LOGIC;

Q : OUT STD_LOGIC );

END COMPONENT;

Q(2) &(o) 90 PC CUCD B01 B12 CD CD CD 811 B13 D Q D Q D Q B21 QN QN QN CK CK CK QN1 QN2 QNO CK (use fdls3ix flip-flops, XOR2 and OR2 gates) Note: Q0, 91, 92 must be of mode inout) Q(2) &(o) 90 PC CUCD B01 B12 CD CD CD 811 B13 D Q D Q D Q B21 QN QN QN CK CK CK QN1 QN2 QNO CK (use fdls3ix flip-flops, XOR2 and OR2 gates) Note: Q0, 91, 92 must be of mode inout)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts