Question: 2. Assume a 2 MB L2 cache with 128-byte blocks and a refill path that is 32 bytes wide. Assume that the L2 can be

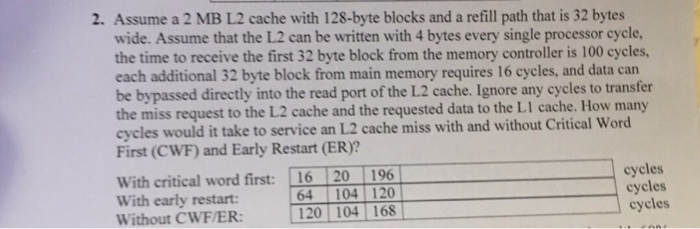

2. Assume a 2 MB L2 cache with 128-byte blocks and a refill path that is 32 bytes wide. Assume that the L2 can be witten with 4 bytes every single processor cycle the time to receive the first 32 byte block from the memory controller is 100 cycles each additional 32 byte block from main memory requires 16 cycles, and data can be bypassed directly into the read port of the L2 cache. Ignore any cycles to transfer the miss request to the L2 cache and the requested data to the LI cache. How many cycles would it take to service an L2 cache mis with and without Critical Word First (CWF) and Early Restart (ER)? With critical word first: 16 20 196 With early restart Without CWF/ER: 64 104 120 120 104 168 cycles cycles cycles

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts